# Power Amplifier, 6 W 2-Channel, Bridge 19 W (Typ)

# **LA4440**

### **Features**

• Built-in 2 Channels (Dual) Enabling Use in Stereo and Bridge Amplifier Applications.

Dual :  $6 \text{ W} \times 2 \text{ (typ)}$ Bridge : 19 W (typ)

- Minimum Number of External Parts Required

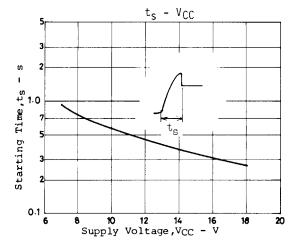

- Small Pop Noise at the Time of Power Supply ON/OFF and Good Starting Balance

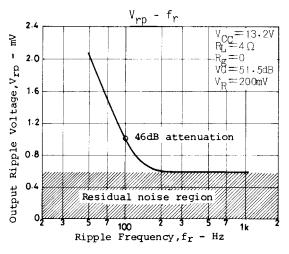

- Good Ripple Rejection: 46 dB (typ)

- Good Channel Separation

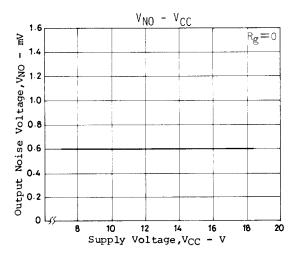

- Small Residual Noise (Rg=0)

- Low Distortion over a Wide Range from Low Frequencies to High Frequencies

- Easy to Design Radiator Fin

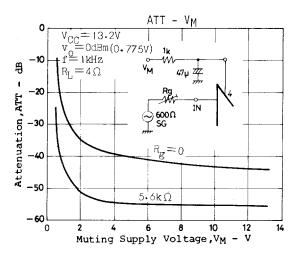

- Built-in Audio Muting Function

- Built-in Protectors

- Thermal Protector

- Overvoltage, Surge Voltage Protector

- ◆ Pin-to-pin Short Protector

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

# ON Semiconductor®

### www.onsemi.com

SIP14 CASE 127AQ

### **MARKING DIAGRAM**

Y = Year of Production

M = Assembly Operation Month

W = Week Number LA4440 = Specific Device Code

### **ORDERING INFORMATION**

| Device    | Package            | Shipping   |

|-----------|--------------------|------------|

| LA4440J-E | SIP14<br>(Pb-Free) | 600 / Tube |

1

### LA4440

### **SPECIFICATIONS**

# ABSOLUTE MAXIMUM RATINGS $(T_A = 25^{\circ}C)$

| Parameter                   | Symbol                  | Conditions                                              | Ratings     | Unit |

|-----------------------------|-------------------------|---------------------------------------------------------|-------------|------|

| Maximum Supply Voltage      | V <sub>CC</sub> max1    | Quiescent (t = 30 s)                                    | 25          | V    |

|                             | V <sub>CC</sub> max2    | Operating                                               | 18          | V    |

| Surge Supply Voltage        | V <sub>CC</sub> (surge) | t ≤ 0.2 s                                               | 50          | V    |

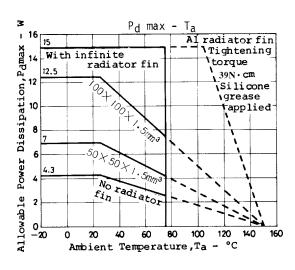

| Allowable Power Dissipation | Pd max                  | $T_C = 75^{\circ}C$ , See Pd max – $T_A$ characteristic | 15          | W    |

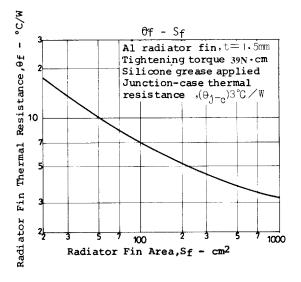

| Thermal Resistance          | θј-с                    | Junction-to-case                                        | 3           | °C/W |

| Operating Temperature       | T <sub>opr</sub>        |                                                         | −20 to +75  | °C   |

| Storage Temperature         | T <sub>stg</sub>        |                                                         | -40 to +150 | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

# RECOMMENDED OPERATING CONDITIONS ( $T_A = 25^{\circ}C$ )

| Parameter       | Symbol          | Conditions | Ratings | Unit |

|-----------------|-----------------|------------|---------|------|

| Supply Voltage  | V <sub>CC</sub> |            | 13.2    | V    |

| Load Resistance | $R_L$           | Stereo     | 2 to 8  | Ω    |

|                 |                 | Bridge     | 4 to 8  | Ω    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

### **OPERATING CHARACTERISTICS**

$(T_A = 25^{\circ}C, V_{CC} = 13.2 \text{ V}, R_L = 4 \text{ W}, f = 1 \text{ kHz}, Rg = 600 \text{ W}, with } 100 \times 100 \times 1.5 \text{ mm}^3 \text{ Al fin, See specified Test Circuit.})$

| Parameter                        | Symbol         | Conditions                                         | Min  | Тур  | Max  | Unit |

|----------------------------------|----------------|----------------------------------------------------|------|------|------|------|

| Quiescent Current                | Icco           |                                                    | -    | 100  | 200  | mA   |

| Voltage Gain                     | VG             |                                                    | 49.5 | 51.5 | 53.5 | dB   |

| Output Power                     | Po             | THD = 10%, Stereo                                  | 5.0  | 6.0  | -    | W    |

|                                  |                | THD = 10%, Bridge                                  | -    | 19   | -    | W    |

| Total Harmonic Distortion        | THD            | P <sub>O</sub> = 1 W                               | -    | 0.1  | 1.0  | %    |

| Input Resistance                 | r <sub>i</sub> |                                                    | -    | 30   | -    | kΩ   |

| Output Noise Voltage             | VNO            | Rg = 0 Ω                                           | -    | 0.6  | 1.0  | mV   |

|                                  |                | Rg = 10 kΩ                                         | -    | 1.0  | 2.0  | mV   |

| Ripple Rejection Ratio           | R <sub>r</sub> | $V_R$ = 200 mV, $f_R$ = 100 Hz,<br>Rg = 0 $\Omega$ | -    | 46   | -    | dB   |

| Channel Separation               | Ch sep         | $V_O = 0$ dBm, $Rg = 10 \text{ k}\Omega$           | 45   | 55   | -    | dB   |

| Muting Attenuation               | ATT            | V <sub>O</sub> = 0 dBm, V <sub>M</sub> = 9 V       | -    | 40   | -    | dB   |

| Gain Difference between Channels | ΔVG            |                                                    | -    | -    | 2    | dB   |

## LA4440

Figure 2.  $S_f$  vs.  $\theta_f$

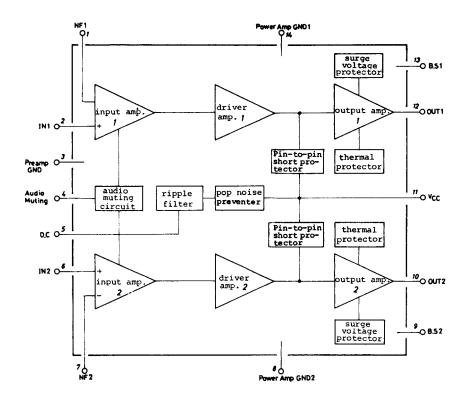

# **EQUIVALENT CIRCUIT BLOCK DIAGRAM**

Figure 3. Equivalent Circuit Block Diagram

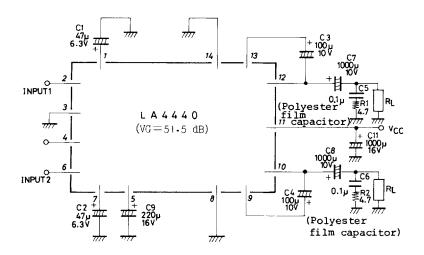

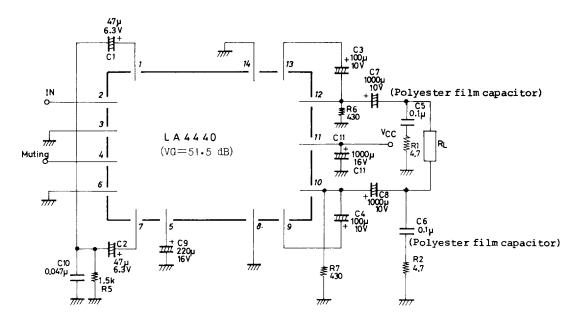

# **SAMPLE APPLICATION CIRCUIT 1 - STEREO USE**

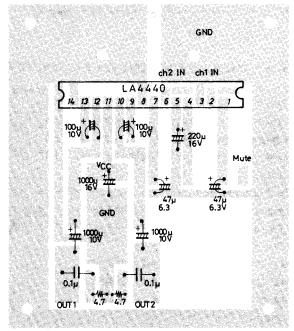

Sample printed circuit pattern for dual mode (Cu-foiled area) 60 x 70 mm<sup>2</sup>

Figure 4. Application Circuit - Stereo Use

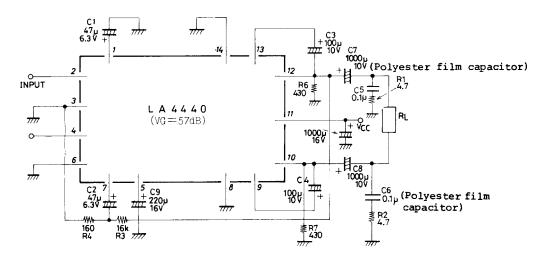

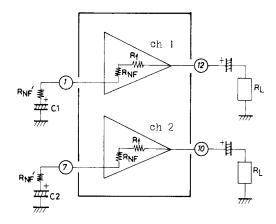

## **SAMPLE APPLICATION CIRCUIT 2 - BRIDGE AMPLIFIER 1**

Figure 5. Application Circuit - Bridge Amplifier 1

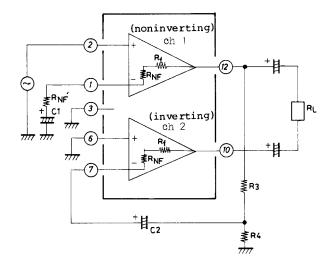

## **SAMPLE APPLICATION CIRCUIT 3 - BRIDGE AMPLIFIER 2**

Figure 6. Application Circuit - Bridge Amplifier 2

### **Description of External Parts**

- C1 (C2) Feedback Capacitor:

The low cutoff frequency depends on this capacitor. If the capacitance value is increased, the starting time is delayed.

- C3 (C4) Bootstrap Capacitor:

If the capacitance value is decreased, the output at low frequencies goes lower.

- C5 (C6) Oscillation Preventing Capacitor:

Polyester film capacitor, being good in temperature characteristic, frequency characteristic, is used.

The capacitance value can be reduced to 0.047 μF depending on the stability of the board.

- C7 (C8) Output Capacitor:

The low cutoff frequency depends on this capacitor.

At the bridge amplifier mode, the output capacitor is generally connected.

- C9 Decoupling Capacitor:

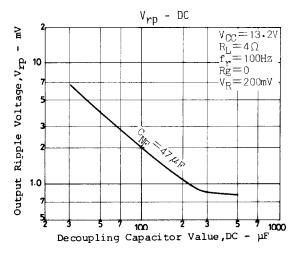

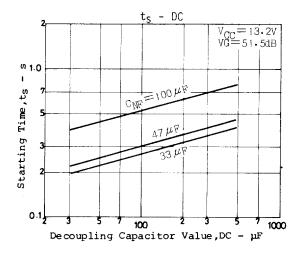

Used for the ripple filter. Since the rejection effect is saturated at a certain capacitance value, it is meaningless to increase the capacitance value more than required. This capacitor, being also used for the time constant of the muting circuit, affects the starting time.

- R1 (R2) Filter resistor for preventing oscillation.

- R3 (R4) Resistor for making input signal of inverting amplifier in Voltage Gain Adjust at Bridge Amplifier Mode (No. 1).

- R5 Resistor for adjusting starting time in Voltage Gain Adjust at Bridge Amplifier Mode (No. 2)

- C10 Capacitor for preventing oscillation in Voltage Gain Adjust at Bridge Amplifier Mode (No. 2)

- C11 Power Source Capacitor

- R6 (R7) Used at bridge amplifier mode in order to increase discharge speed and to secure transient stability.

# Feaures of IC System and Functions of Remaining Pins

- a. Since the input circuit uses PNP transistors and the input potential is designed to be 0 bias, no input coupling capacitor is required and direct coupling is available. However, when slider contact noise caused by the variable resistor presents a problem, connect an capacitor in series with the input.

- b. The open-loop voltage gain is lowered and the negative feedback amount is reduced for stabilization. An increase in distortion resulted from the reduced negative feedback amount is avoided by use of the built-in unique distortion reduction circuit, and thus distortion is kept at 0.1% (typ.).

- c. A capacitor for oscillation compensation is contained as a means of reducing the number of external parts. The capacitance value is 35 pF which determines high cutoff frequency  $f_H$  (-3 dB point) of the amplifier ( $f_H \approx 20 \text{ kHz}$ ).

- d. For preventing the IC from being damaged by a surge applied on the power line, an overvoltage protector is contained. Overvoltage setting is 25 V. It is capable of withstanding up to 50 V at giant pulse surge 200 ms.

- e. No damege occurs even when power is applied at a state where pins 10, 11, and 12 are short-circuited with solder bridge, etc.

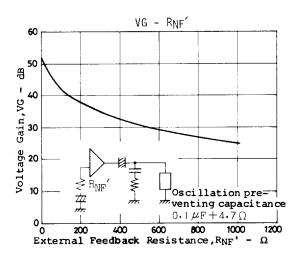

- f. To minimize the variations in voltage gain, feedback resistor  $R_{\rm NF}$  is contained and voltage gain (51.5 dB) is fixed.

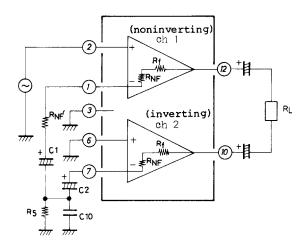

Voltage Gain Adjust at Stereo Mode:

$R_{NF}$  = 50  $\Omega$  (typ),  $R_f$  = 20 k $\Omega$  (typ) At  $R_{NF}$ ' = 0 (recommended VG)

$$VG = 20 \log \frac{VG}{R_{NF}} (dB)$$

(eq. 1)

In case of using RNF'

$$VG = 20 \log \frac{R_f}{R_{NE} + R_{NE}}$$

(dB) (eq. 2)

Voltage Gain Adjust at Bridge Amplifier Mode (No. 1)

The bridge amplifier configuration is as shown left, in which ch1 and ch2 operate as noninverting amplifier and inverting amplifier respectively.

The output of the noninverting amplifier divided by resistors R3, R4 is applied, as input, to the inverting amplifier.

Since attenuation (R4/R3) of the non-inverting amplifier output and amplification factor ( $R_f/R4+R_{NF}$ ) of the inverting amplifier are fixed to be the same, signals of the same level and 1805 out of phase with each other can be obtained at output pins (12) and (10). The total voltage gain is apparently higher than that of the noninverting amplifier by 6 dB and is approximately calculated by the following formula.

$$VG = 20 \log \frac{R_f}{R_{NF}} + 6 dB$$

(eq. 3)

In case of reducing the voltage gain, RNF' is connected to the noninverting amplifier side only and the following formula is used.

$$VG = 20 \log \frac{R_f}{R_{NF} + R_{NF}'} + 6 dB$$

(eq. 4)

Voltage Gain Adjust at Bridge Amplifier Mode (No. 2)

VG =

$$20 \log \frac{R_f}{R_{NF} + \frac{R_{NF}}{2}}$$

(dB) (eq. 5)

where  $(R_{NF} + R_{NF}') \ll R5$

From this formula, it is seen that connecting  $R_{NF}$ ' causes the voltage gain to be reduced at the modes of both stereo amplifier and bridge amplifier.

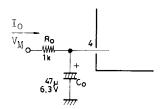

g. In case of applying audio muting in each application circuit, the following circuit is used.

$6 \text{ V} \leq \text{V}_{\text{M}} \leq \text{V}_{\text{CC}}$  Recommended  $\text{V}_{\text{M}} = 9 \text{ V}$   $\text{A}_{\text{TT}} = 40 \text{ dB } (\text{Rg} = 600 \Omega)$

Flow-in current IO is calculated by the following formula.

$$I_{O} = \frac{V_{M} - V_{BE}}{R_{O}}$$

(eq. 6)

In case of increasing the muting attenuation, resistor  $5.6~k\Omega$  is connected in series with the input, and then the attenuation is made to be 55~dB. Be careful that connecting an input capacitor causes pop noise to be increased at the time of application of AC muting. Increased  $R_O$ ,  $C_O$  make it possible to reduce the noise. In case of completely cutting off power IC, pin (5) is grounded, and then DC control is available and the attenuation is made to be  $\infty$ .

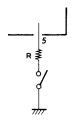

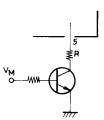

General-purpose switch

Transistor switch

Stereo:  $20 \Omega \le R \le 100 \Omega$ Bridge No.1:  $20 \Omega \le R \le 100 \Omega$ Bridge No. 2:  $0 \Omega \le R \le 50 \Omega$

Table 1. PIN VOLTAGE (UNIT: V)

|                                  |        |        | ,          |                       |      |        |        |                     |        |            |      |            |        |                     |

|----------------------------------|--------|--------|------------|-----------------------|------|--------|--------|---------------------|--------|------------|------|------------|--------|---------------------|

| Pin No.                          | 1      | 2      | 3          | 4                     | 5    | 6      | 7      | 8                   | 9      | 10         | 11   | 12         | 13     | 14                  |

| Function Pin                     | CH1 NF | CH1 NF | Pre<br>GND | AC<br>Audio<br>Muting | DC   | CH2 IN | CH2 NF | CH2<br>Power<br>GND | CH2 BS | CH2<br>OUT | VCC  | CH1<br>OUT | CH1 BS | CH1<br>Power<br>GND |

| Pin Voltage at<br>Quiescent Mode | 1.4    | 0.03   | 0          | 0                     | 13.0 | 0.03   | 1.4    | 0                   | 11.9   | 6.8        | 13.2 | 6.8        | 11.9   | 0                   |

### **Proper Cares in Using IC**

- Maximum Ratings:

- If the IC is used in the vicinity of the maximum ratings, even a slight variation in conditions may cause the maximum ratings to be exceeded, thereby leading to breakdown. Allow an ample margin of variation for supply voltage, etc. and use the IC in the range where the maximum ratings are not exceeded.

- Printed Circuit Board:

100

10

1.0

Total Harmonic Distortion, THD

When making the board, refer to the sample printed circuit pattern and be careful that no feedback loop is formed between input and output.

• Oscillation Preventing Capacitor:

Normally, a polyester film capacitor is used for 0.1 µF +  $4.7 \Omega$ . The capacitance value can be reduced to  $0.047 \, \mathrm{F}$ depending on the stability of the board.

• Others:

Connect the radiator fin of the package to GND.

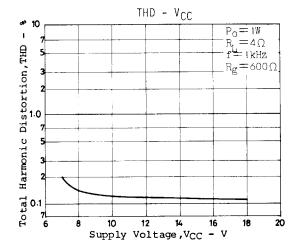

### CHARACTERISTICS AT STEREO AMPLIFIER MODE

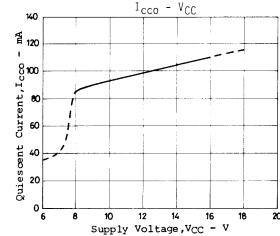

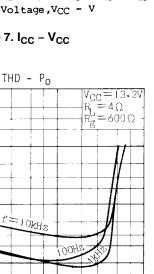

Figure 7.  $I_{CC}$  –  $V_{CC}$

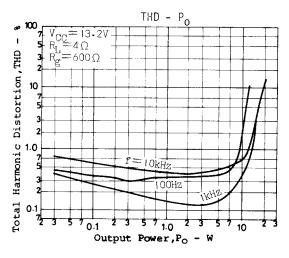

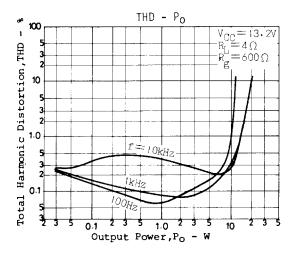

Figure 9. THD - Po

Output Power, Po

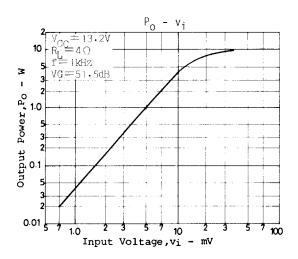

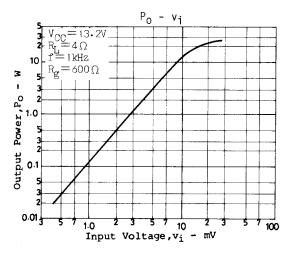

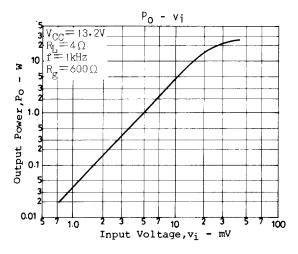

Figure 8. Po - Vi

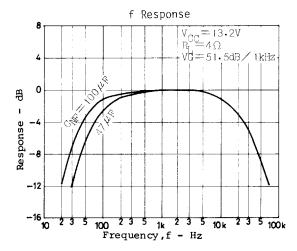

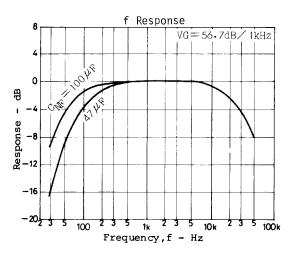

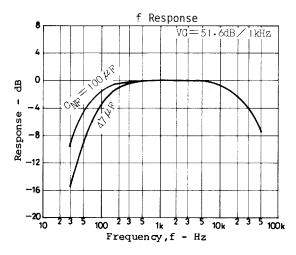

Figure 10. f Response

# **CHARACTERISTICS AT STEREO AMPLIFIER MODE (Continued)**

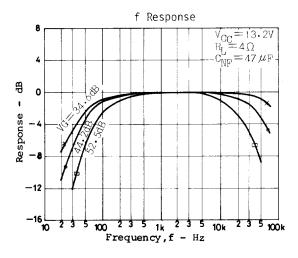

Figure 11. f Response

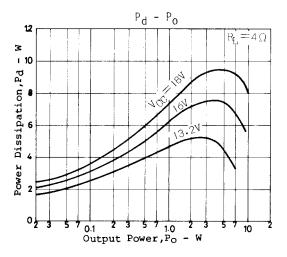

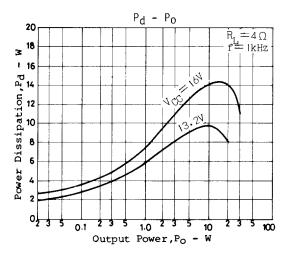

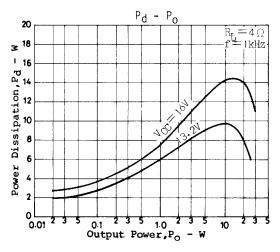

Figure 13. P<sub>d</sub> - P<sub>O</sub>

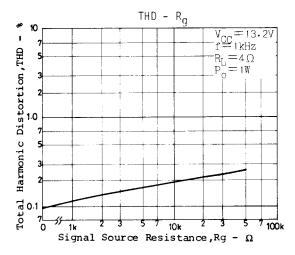

Figure 15. THD - Rg

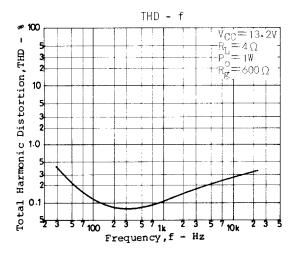

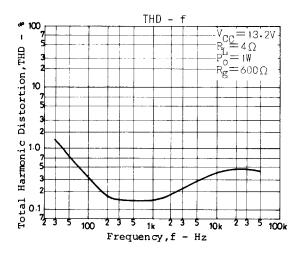

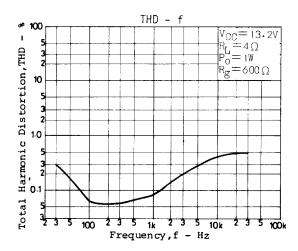

Figure 12. THD - f

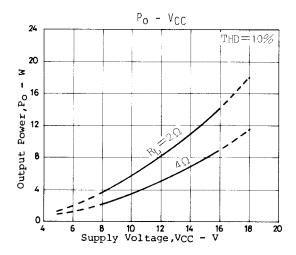

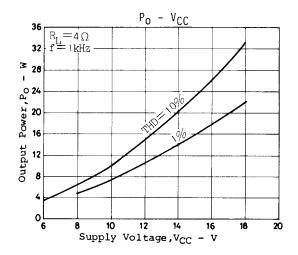

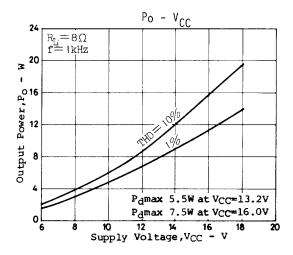

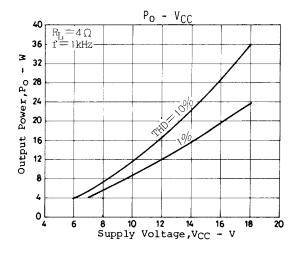

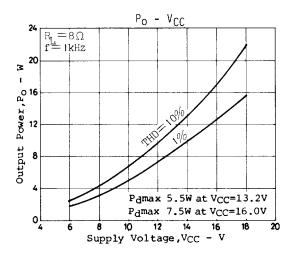

Figure 14. Po - Vcc

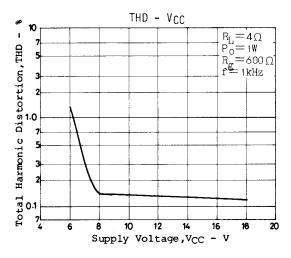

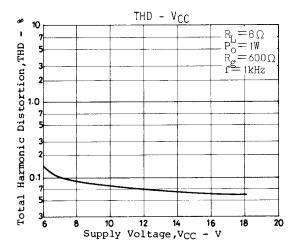

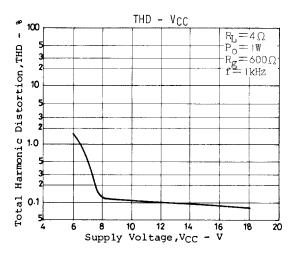

Figure 16. THD - V<sub>CC</sub>

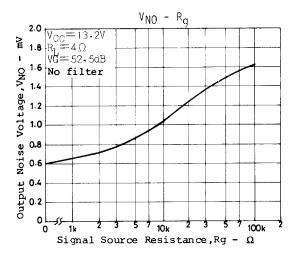

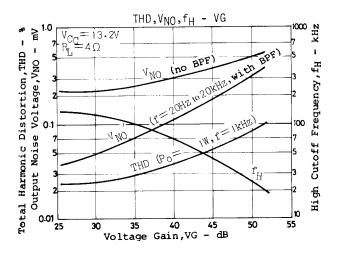

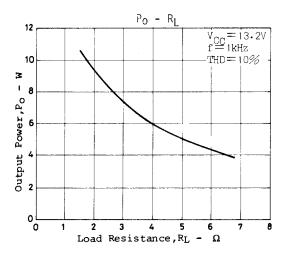

# **CHARACTERISTICS AT STEREO AMPLIFIER MODE (Continued)**

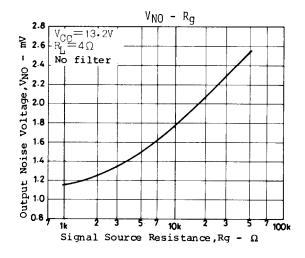

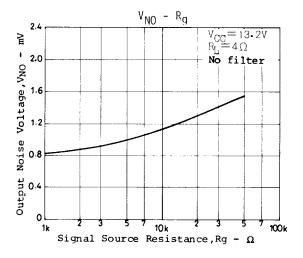

Figure 17.  $V_{NO}$  –  $R_{g}$

Figure 19. THD,  $V_{NO}$ ,  $f_H - V_G$

Figure 21. Po - RL

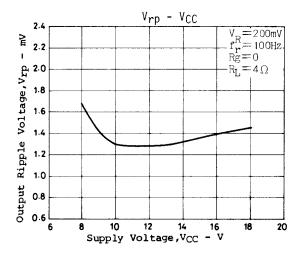

Figure 18. V<sub>NO</sub> - V<sub>CC</sub>

Figure 20. V<sub>G</sub> - R<sub>NF</sub>'

Figure 22. t<sub>S</sub> - V<sub>CC</sub>

# **CHARACTERISTICS AT STEREO AMPLIFIER MODE (Continued)**

Figure 23. ATT<sub>O</sub> - V<sub>M</sub>

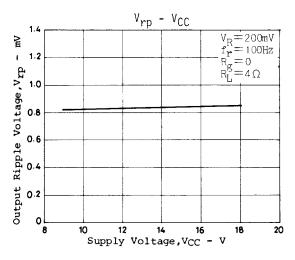

Figure 25. V<sub>rp</sub> – DC

Figure 24. V<sub>rp</sub> – f<sub>r</sub>

Figure 26. t<sub>S</sub> - DC

### **CHARACTERISTICS AT BRIDGE AMPLIFIER MODE NO. 1**

Figure 27. P<sub>O</sub> – V<sub>i</sub>

Figure 29. f Response

Figure 31. P<sub>d</sub> - P<sub>O</sub>

Figure 28. THD - Po

Figure 30. THD - f

Figure 32. Po - V<sub>CC</sub>

# **CHARACTERISTICS AT BRIDGE AMPLIFIER MODE NO. 1 (Continued)**

Figure 33. THD - V<sub>CC</sub>

Figure 35. Vrp - V<sub>CC</sub>

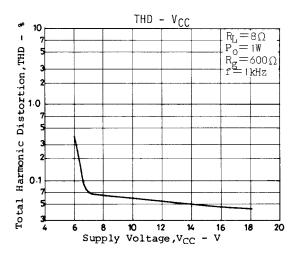

Figure 37. THD - V<sub>CC</sub>

Figure 34.  $V_{NO}$  –  $R_{g}$

Figure 36. Po - Vcc

## **CHARACTERISTICS AT BRIDGE AMPLIFIER MODE NO. 2**

Figure 38. Po - Vi

Figure 40. f Response

Figure 42. P<sub>d</sub> - P<sub>O</sub>

Figure 39. THD - Po

Figure 41. THD - f

Figure 43. Po - Vcc

# **CHARACTERISTICS AT BRIDGE AMPLIFIER MODE NO. 2 (Continued)**

Figure 44. THD - V<sub>CC</sub>

Figure 46. Vrp - V<sub>CC</sub>

Figure 48. THD - V<sub>CC</sub>

Figure 45. V<sub>NO</sub> - R<sub>g</sub>

Figure 47. Po - Vcc

### LA4440

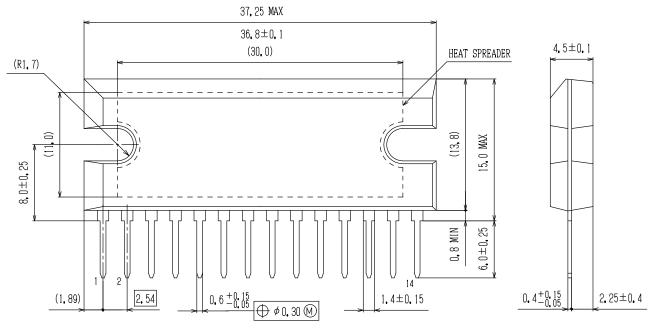

## **Proper Cares in Mounging Radiator Fin**

- 1. The mounting torque is in the range of 39 to  $59N \cdot cm$ .

- 2. The distance between screw holes of the radiator fin must coincide with the distance between screw holes of the IC.

With case outline dimensions L and R referred to, the screws must be tightened with the distance between them as close to each other as possible.

- 3. The screw to be used must have a head equivalent to the one of truss machine screw or binder machine screw defined by JIS. Washers must be also used to protect the IC case.

- 4. No foreign matter such as cutting particles shall exist between heat sink and radiator fin. When applying grease on the junction surface, it must be applied uniformly on the whole surface.

- 5. IC lead pins are soldered to the printed circuit board after the radiator fin is mounted on the IC.

### SIP14 36.8x13.8 / SIP14H CASE 127AQ ISSUE A

**DATE 23 OCT 2013**

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code

Y = Year

M = Month

DDD = Additional Traceability Data

\*This information is generic. Please refer to

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot " ■", may or may not be present.

| DESCRIPTION:     | SIP14 / SIP14H 36.8X13.8  |                                                                      | PAGE 1 OF 2 |  |

|------------------|---------------------------|----------------------------------------------------------------------|-------------|--|

| NEW STANDARD:    |                           | "CONTROLLED COPY" in red.                                            |             |  |

| STATUS:          | ON SEMICONDUCTOR STANDARD | accessed directly from the Document versions are uncontrolled except |             |  |

| DOCUMENT NUMBER: | 98AON66039E               | Electronic versions are uncontrolle                                  | •           |  |

| N | Semiconductor® | ON |

|---|----------------|----|

|   |                |    |

DOCUMENT NUMBER: 98AON66039E

PAGE 2 OF 2

| SSUE | REVISION                                                                                  | DATE        |

|------|-------------------------------------------------------------------------------------------|-------------|

| 0    | RELEASED FOR PRODUCTION FROM SANYO ENACT# S-158 TO ON SEMICONDUCTOR. REQ. BY D. TRUHITTE. | 30 DEC 2011 |

| Α    | ADDED GENERIC MARKING DIAGRAM. REQ. BY D. TRUHITTE.                                       | 23 OCT 2013 |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

|      |                                                                                           |             |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

© Semiconductor Components Industries, LLC, 2013

Case Outline Number:

October, 2013 – Rev. A

127AQ

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative