LMX2492, LMX2492-Q1

ZHCSCB6-MARCH 2014

# LMX2492/LMX2492-Q1 14GHz 低噪声分数 N 分频锁相环 (PLL), 坡/超宽带信号源发生功能

### 特性

- -227dBc/Hz 标称 PLL 噪声

- 500MHz 14GHz 宽频带 PLL

- 3.15 -5.25V 电荷泵 PLL 电源

- 多用途斜坡/超宽带信号源发生

- 最大相位检测器频率 200MHz

- 频移键控/相移键控 (FSK/PSK) 调制引脚

- 数字锁检测

- 单个 3.3V 电源

- 汽车用 125°C Q100 1 级认证

- 非汽车用 (LMX2492) 选项

#### 2 应用范围

- 汽车用调频连续波 (FMCW) 雷达

- 军用雷达

- 微波回程

- 测试和测量

- 卫星通信

- 无线基础设施

- 针对高速模数转换器 (ADC) / 数模转换器 (DAC) 的 采样时钟

### 3 说明

LMX2492/92-Q1 是一款具有斜坡和超宽带信号源发生 功能的 14GHz 宽频带三角积分分数 N 分频 PLL。 它 由一个相位频率检测器、可编程电荷泵以及用于外部 VCO 的高频输入组成。 LMX2492/92-Q1 支持宽范围 且灵活的斜升功能类 (class of ramping capabilities), 其中包括 FSK, PSK 和高达 8 个段的可配置分段线性 FM 调制系统配置。 它还支持精细的 PLL 分辨率以及 相位检测器速率高达 200MHz 的快速斜坡。 LMX2492/92-Q1 的任何一个寄存器均可被回读。 LMX2492/92-Q1 可由单个 3.3V 电源供电运行。 而

目,对于电压高达 5.25V 的电荷泵的支持能够免除对 于外部放大器的需要,从而获得一个具有更佳相位噪声 性能的更简单解决方案。

#### 器件信息

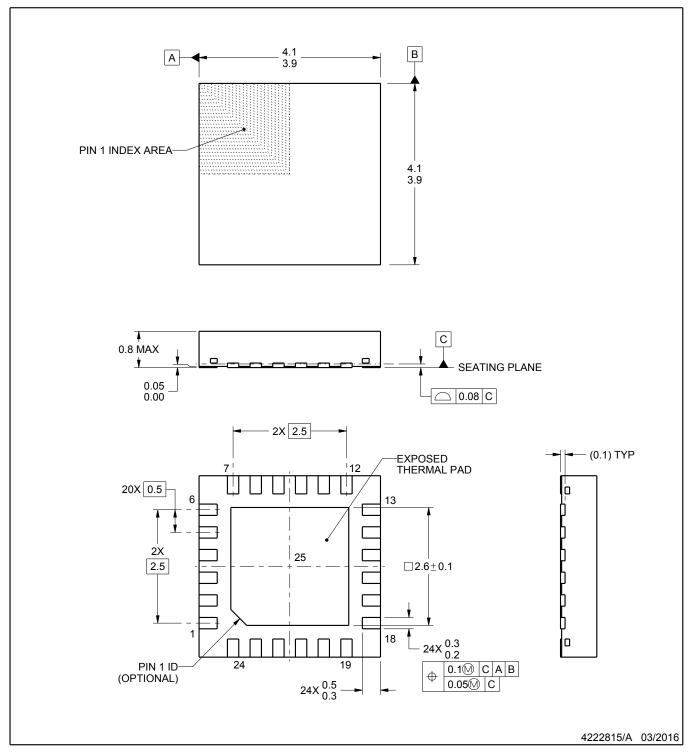

| 订货编号          | 封装                | 封装尺寸      |

|---------------|-------------------|-----------|

| LMX2492-Q1RTW | 超薄四方扁平无           |           |

| LMX2492RTW    | 引线 (WQFN)<br>(24) | 4mm x 4mm |

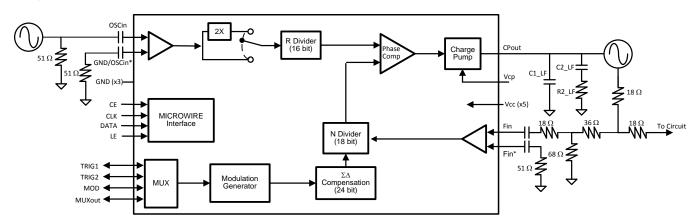

# 简化电路原理图

www.ti.com.cn

# 目录

|   | 4.+. kd.                                             |    | 9.6. Degister Men                             | 4.4 |

|---|------------------------------------------------------|----|-----------------------------------------------|-----|

| 1 | 特性                                                   |    | 8.6 Register Map                              |     |

| 2 | 应用范围 1                                               |    | 8.7 Register Field Descriptions               |     |

| 3 | 说明 1                                                 |    | 8.8 Lock Detect and Charge Pump Monitoring    |     |

| 4 | 简化电路原理图1                                             |    | 8.9 TRIG1,TRIG2,MOD, and MUXout Pins          | 22  |

| 5 | 修订历史记录 2                                             |    | 8.10 Ramping Functions                        |     |

| 6 | Terminal Configuration and Functions                 |    | 8.11 Individual Ramp Controls                 | 26  |

|   | _                                                    | 9  | Applications and Implementation               | 27  |

| 7 | Specifications4                                      |    | 9.1 Application Information                   | 27  |

|   | 7.1 Absolute Maximum Ratings                         |    | 9.2 Typical Applications                      |     |

|   | 7.2 Handling Ratings4                                | 10 | Power Supply Recommendations                  |     |

|   | 7.3 Recommended Operating Conditions4                | 11 | Layout                                        |     |

|   | 7.4 Thermal Information4                             |    |                                               |     |

|   | 7.5 Electrical Characteristics 5                     |    | ,                                             |     |

|   | 7.6 Timing Requirements, Programming Interface (CLK, |    | 11.2 Layout Example                           |     |

|   | DATA, LE)6                                           | 12 | Device and Documentation Support              |     |

|   | 7.7 Serial Data Input Timing 6                       |    | 12.1 Device Support                           | 35  |

|   | 7.8 Typical Characteristics                          |    | 12.2 Documentation Support                    | 35  |

| 8 | Detailed Description9                                |    | 12.3 Related Links                            | 35  |

|   | 8.1 Overview 9                                       |    | 12.4 Trademarks                               | 35  |

|   | 8.2 Functional Block Diagram9                        |    | 12.5 Electrostatic Discharge Caution          | 35  |

|   | 8.3 Feature Description9                             |    | 12.6 Glossary                                 | 35  |

|   | 8.4 Device Functional Modes                          | 13 | 机械封装和可订购信息                                    | 35  |

|   | 8.5 Programming                                      |    | P = 5/4 - 4 - 4 - 4 - 4 - 4 - 4 - 4 - 4 - 4 - |     |

|   | 0.0 1 Togramming                                     |    |                                               |     |

# 5 修订历史记录

| 日期      | 修订版本 | 注释      |

|---------|------|---------|

| 2014年3月 | *    | 最初发布版本。 |

www.ti.com.cn ZHCSCB6 – MARCH 2014

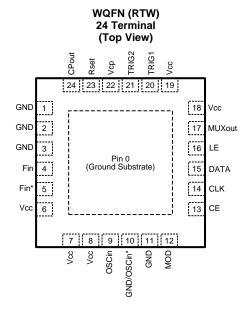

# 6 Terminal Configuration and Functions

### **Terminal Functions**

| TERMINAL NUMBER NAME |                | TVDE         | DECORPTION                                                                                                                                                                              |  |  |

|----------------------|----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                      |                | TYPE         | DESCRIPTION                                                                                                                                                                             |  |  |

| 0                    | DAP            | GND          | Die Attach Pad. Connect to PCB ground plane.                                                                                                                                            |  |  |

| 1                    | GND            | GND          | Ground for charge pump.                                                                                                                                                                 |  |  |

| 2,3                  | GND            | GND          | Ground for Fin Buffer                                                                                                                                                                   |  |  |

| 4,5                  | Fin<br>Fin*    | Input        | Complimentary high frequency input pins. Should be AC coupled. If driving single-ended, impedance as seen from Fin and Fin* pins looking outwards from the part should be roughly same. |  |  |

| 6                    | Vcc            | Supply       | Power Supply for Fin Buffer                                                                                                                                                             |  |  |

| 7                    | Vcc            | Supply       | Supply for On-chip LDOs                                                                                                                                                                 |  |  |

| 8                    | Vcc            | Supply       | Supply for OSCin Buffer                                                                                                                                                                 |  |  |

| 9                    | OSCin          | Input        | Reference Frequency Input                                                                                                                                                               |  |  |

| 10                   | GND/<br>OSCin* | GND/Input    | Complimentary input for OSCin. If not used, it is recommended to match the termination as seen from the OSCin terminal looking outwards. However, this may also be grounded as well.    |  |  |

| 11                   | GND            | GND          | Ground for OSCin Buffer                                                                                                                                                                 |  |  |

| 12                   | MOD            | Input/Output | Multiplexed Input/Output Pins for Ramp Triggers, FSK/PSK Modulation, FastLock, and Diagnostics                                                                                          |  |  |

| 13                   | CE             | Input        | Chip Enable                                                                                                                                                                             |  |  |

| 14                   | CLK            | GND          | Serial Programming Clock.                                                                                                                                                               |  |  |

| 15                   | DATA           | GND          | Serial Programming Data                                                                                                                                                                 |  |  |

| 16                   | LE             | Input        | Serial Programming Latch Enable                                                                                                                                                         |  |  |

| 17                   | MUXout         | Input/Output | Multiplexed Input/Output Pins for Ramp Triggers, FSK/PSK Modulation, FastLock, and Diagnostics                                                                                          |  |  |

| 18                   | Vcc            | Supply       | Supply for delta sigma engine.                                                                                                                                                          |  |  |

| 19                   | Vcc            | Supply       | Supply for general circuitry.                                                                                                                                                           |  |  |

| 20                   | TRIG1          | Input/Output | Multiplexed Input/Output Pins for Ramp Triggers, FSK/PSK Modulation, FastLock, and Diagnostics                                                                                          |  |  |

| 21                   | TRIG2          | Input/Output | Multiplexed Input/Output Pins for Ramp Triggers, FSK/PSK Modulation, FastLock, and Diagnostics                                                                                          |  |  |

| 22                   | Vcp            | Supply       | Power Supply for the charge pump.                                                                                                                                                       |  |  |

| 23                   | Rset           | NC           | No connect.                                                                                                                                                                             |  |  |

| 24                   | CPout          | Output       | Charge Pump Output                                                                                                                                                                      |  |  |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                       |                                     | MIN  | MAX       | UNIT |

|-----------------------|-------------------------------------|------|-----------|------|

| Vcp                   | Supply Voltage for Charge Pump      | Vcc  | 5.5       | V    |

| CPout                 | Charge Pump Output Pin              | -0.3 | Vcp       | V    |

| Vcc                   | All Vcc Pins                        | -0.3 | 3.6       | V    |

| Others                | All Other I/O Pins                  | -0.3 | Vcc + 0.3 | V    |

| T <sub>Solder</sub>   | Lead Temperature (solder 4 seconds) |      | 260       | °C   |

| T <sub>Junction</sub> | Junction Temperature                |      | 150       | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 Handling Ratings

|                                 |                                                              | MIN | MAX  | UNIT |

|---------------------------------|--------------------------------------------------------------|-----|------|------|

| T <sub>STG</sub>                | Storage Temperature Range                                    | -65 | 150  | °C   |

| MSL                             | Moisture Sensitivity Level                                   |     | 3    | n/a  |

| v (1)                           | Human body model (HBM) ESD stress voltage (2)                |     | 2500 | V    |

| V <sub>ESD</sub> <sup>(1)</sup> | Charged device model (CDM) ESD stress voltage <sup>(3)</sup> |     | 1500 | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges in to the device.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

| SYMBOL | PARAMETER                  | DEVICE     | MIN  | TYP | MAX  | UNIT |

|--------|----------------------------|------------|------|-----|------|------|

| Vcc    | PLL Supply Voltage         |            | 3.15 | 3.3 | 3.45 | V    |

| Vcp    | Charge Pump Supply Voltage |            | Vcc  |     | 5.25 | V    |

| _      | Ambient Temperature        | LMX2492    | -40  |     | 85   | ٥°   |

| 1A     | Ambient Temperature        | LMX2492-Q1 | -40  |     | 125  |      |

| _      | lunction Townserture       | LMX2492    | -40  |     | 125  | °C   |

| IJ     | Junction Temperature       | LMX2492-Q1 | -40  |     | 135  | °C   |

#### 7.4 Thermal Information

|                 | THERMAL METRIC <sup>(1)</sup>                | Temperature | UNIT |

|-----------------|----------------------------------------------|-------------|------|

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance       | 39.4        |      |

| $R_{\theta JC}$ | Junction-to-case thermal resistance          | 7.1         | °C/W |

| ΨЈВ             | Junction-to-board characterization parameter | 20          |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250 V CDM allows safe manufacturing with a standard ESD control process.

ZHCSCB6-MARCH 2014 www.ti.com.cn

#### 7.5 Electrical Characteristics

(3.15 V ≤ Vcc ≤ 3.45 V. Vcc ≤Vcp ≤5.25 V. Typical values are at Vcc = Vcp = 3.3 V, 25 °C. -40°C ≤  $T_A$  ≤ 85 °C for the LMX2492 and -40°C ≤  $T_A$  ≤ 125 °C for the LMX2492-Q1; except as specified.)

| SYMBOL                 | PARAMETER                                  | COI                           | CONDITIONS             |    | TYP  | MAX     | UNIT   |  |

|------------------------|--------------------------------------------|-------------------------------|------------------------|----|------|---------|--------|--|

|                        |                                            |                               | Fpd = 10 MHz           |    | 45   |         |        |  |

|                        |                                            | All Vcc Pins                  | Fpd = 100 MHz          |    | 50   |         | mA     |  |

| laa                    | Comment Commenting                         |                               | Fpd = 200 MHz          |    | 55   |         |        |  |

| Icc                    | Current Consumption                        |                               | Kpd = 0.1 mA           |    | 2    |         |        |  |

|                        |                                            | Vcp Pin                       | Kpd = 1.6 mA           |    | 10   |         |        |  |

|                        |                                            |                               | Kpd = 3.1 mA           |    | 19   |         |        |  |

| IccPD                  | Current                                    | POWERDOWN                     |                        |    | 3    |         |        |  |

|                        |                                            | OSC_DIFFR=0,                  | Doubler Disabled       | 10 |      | 600     |        |  |

| 4                      | Frequency for OSCin terminal               | OSC_DIFFR=0, Doubler Enabled  |                        | 10 |      | 300     | MHz    |  |

| f <sub>OSCin</sub>     |                                            | OSC_DIFFR=1, Doubler Disabled |                        | 10 |      | 1200    |        |  |

|                        |                                            | OSC_DIFFR=1, Doubler Enabled  |                        | 10 |      | 600     |        |  |

| V <sub>OSCin</sub>     | Voltage for OSCin Pin <sup>(1)</sup>       |                               |                        |    |      | Vcc-0.5 | Vpp    |  |

| f <sub>Fin</sub>       | Frequency for FinPin <sup>(2)</sup>        |                               |                        |    |      | 14000   | MHz    |  |

| p <sub>Fin</sub>       | Power for Fin Pin                          | Single-Ended Op               | eration                | -5 |      | 5       | dBm    |  |

| $f_{PD}$               | Phase Detector Frequency                   |                               |                        |    |      | 200     | MHz    |  |

| PN1Hz                  | PLL Figure of Merit <sup>(3)</sup>         |                               |                        |    | -227 |         | dBc/Hz |  |

| PN10kHz                | Normalized PLL 1/f<br>Noise <sup>(3)</sup> | Normalized to 10 carrier.     | kHz offset for a 1 GHz |    | -120 |         | dBc/Hz |  |

| I <sub>CPout</sub> TRI | Charge Pump Leakage Tristate Leakage       |                               |                        |    |      | 10      | nA     |  |

| I <sub>CPout</sub> MM  | Charge Pump Mismatch (4)                   | V <sub>CPout</sub> = Vcp / 2  |                        |    | 5 %  |         |        |  |

|                        |                                            |                               | CPG=1X                 |    | 0.1  |         |        |  |

| I <sub>CPout</sub>     | Charge Pump Current                        | V <sub>CPout</sub> = Vcp / 2  |                        |    |      |         | mA     |  |

|                        |                                            |                               |                        |    | 3.1  |         |        |  |

|                        |                                            |                               |                        |    |      |         |        |  |

For optimal phase noise performance, higher input voltage and a slew rate of at least 3 V/ns is recommended

Tested to 13.5 GHz, Guaranteed to 14 GHz by characterization

PLL Noise Metrics are measured with a clean OSCin signal with a high slew rate using a wide loop bandwidth. The noise metrics model the PLL noise for an infinite loop bandwidth as: PLL\_Total = 10xlog( 10<sup>PLL\_Flat/10</sup> + 10<sup>PLL\_Flicker(Offset)/10</sup>)

PLL\_Flat = PN1Hz + 20xlog(N) + 10xlog(Fpd/1Hz)

PLL\_Flicker = PN10kHz - 10xlog(Offset/10kHz) + 20xlog(Fvco/1GHz)

<sup>(4)</sup> Charge pump mismatch varies as a function of charge pump voltage. Consult typical performance characteristics to see this variation.

www.ti.com.cn

### **Electrical Characteristics (continued)**

(3.15 V  $\leq$  Vcc  $\leq$  3.45 V. Vcc  $\leq$ Vcp  $\leq$ 5.25 V. Typical values are at Vcc = Vcp = 3.3 V, 25 °C.

-40°C ≤  $T_A$  ≤ 85 °C for the LMX2492 and -40°C ≤  $T_A$  ≤ 125 °C for the LMX2492-Q1; except as specified.)

| SYMBOL               | PARAMETER               | CONDITIONS                    | MIN          | TYP | MAX       | UNIT |

|----------------------|-------------------------|-------------------------------|--------------|-----|-----------|------|

| LOGIC OUT            | PUT TERMINALS (MUXout,1 | RIG1,TRIG2,MOD)               |              |     |           |      |

| V <sub>OH</sub>      | Output High Voltage     |                               | 0.8 x<br>Vcc | Vcc |           | V    |

| V <sub>OL</sub>      | Output Low Voltage      |                               |              | 0   | 0.2 x Vcc | V    |

| LOGIC INPU           | JT TERMINALS (CE,CLK,DA | TA,LE,MUXout,TRIG1,TRIG2,MOD) |              |     |           |      |

| V <sub>IH</sub>      | Input High Voltage      |                               | 1.4          |     | Vcc       | V    |

| V <sub>IL</sub>      | Input Low Voltage       |                               | 0            |     | 0.6       | V    |

| I <sub>IH</sub>      | Input Leakage           |                               | -5           | 1   | 5         | uA   |

| T <sub>CE</sub> LOW  | Chip enable Low Time    |                               | 5            |     |           | us   |

| T <sub>CE</sub> HIGH | Chip enable High Time   |                               | 5            |     |           | us   |

|                      |                         |                               |              |     |           |      |

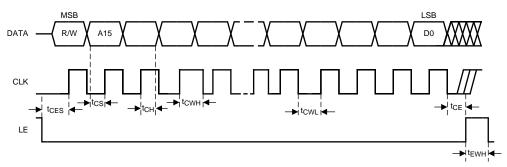

7.6 Timing Requirements, Programming Interface (CLK, DATA, LE)

| SYMBOL           | PARAMETER                  | MIN | TYP MAX | UNIT |

|------------------|----------------------------|-----|---------|------|

| T <sub>CE</sub>  | Clock To LE Low Time       | 35  |         | ns   |

| T <sub>CS</sub>  | Data to Clock Setup Time   | 10  |         | ns   |

| T <sub>CH</sub>  | Data to Clock Hold Time    | 10  |         | ns   |

| T <sub>CWH</sub> | Clock Pulse Width High     | 25  |         | ns   |

| T <sub>CWL</sub> | Clock Pulse Width Low      | 25  |         | ns   |

| T <sub>CES</sub> | Enable to Clock Setup Time | 10  |         | ns   |

| T <sub>EWH</sub> | Enable Pulse Width High    | 10  |         | ns   |

# 7.7 Serial Data Input Timing

There are several other considerations for programming:

- The DATA is clocked into a shift register on each rising edge of the CLK signal. On the rising edge of the LE signal, the data is sent from the shift register to an actual counter.

- If no LE signal is given after the last data bit and the clock is kept toggling, then these bits will be read into the next lower register. This eliminates the need to send the address each time.

- A slew rate of at least 30 V/us is recommended for the CLK, DATA, and LE signals

- Timing specs also apply to readback. Readback can be done through the MUXout, TRIG1, TRIG2, or MOD terminals.

www.ti.com.cn ZHCSCB6 – MARCH 2014

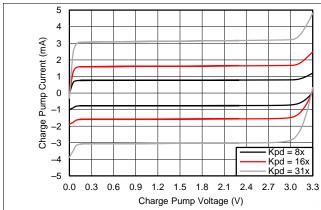

## 7.8 Typical Characteristics

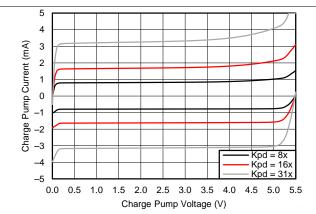

For a charge pump supply of 3.3 V, optimal performance is for a typical charge pump output voltage between 0.5 and 2.8 volts.

Figure 1. Charge Pump Current for Vcp = 3.3 V

For a charge pump supply voltage of 5 volts or higher, optimal performance is typically for a charge pump output voltage between 0.5 and 4.5 volts.

Figure 2. Charge Pump Current for Vcp = 5.5 V

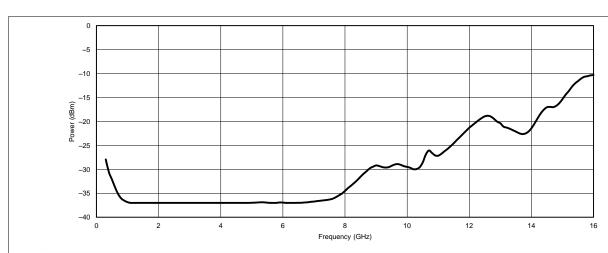

Typical value of lowest power level as a function of frequency. Design to electrical specifications for input sensitivity, not typical performance graphs.

Figure 3. Fin Input Sensitivity

# **Typical Characteristics (continued)**

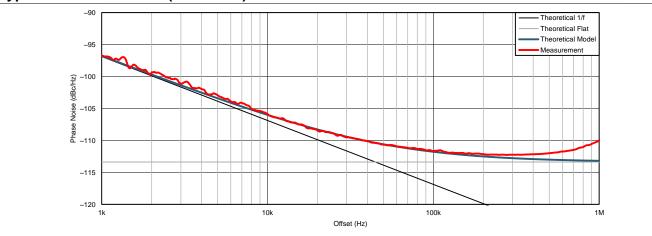

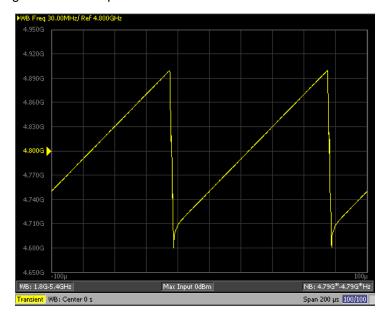

This plot is for a phase detector of 100 MHz, 2 MHz loop bandwidth, and VCO at 9600 MHz. However, the plot shown is the divide by 2 port at 4800 MHz. The input was a 100 MHz Wenzel Oscillator. The model shows this phase noise has a figure of merit of -227 dBc/Hz and a normalized 1/f noise of -120.5 dBc/Hz. The charge pump supply was 5 V and the charge pump output voltage was 1.34 V.

Figure 4. LMX2492/92-Q1 Phase Noise for Fpd =100 MHz, Fvco = 9600 MHz/2

### 8 Detailed Description

#### 8.1 Overview

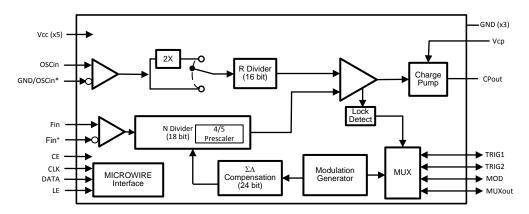

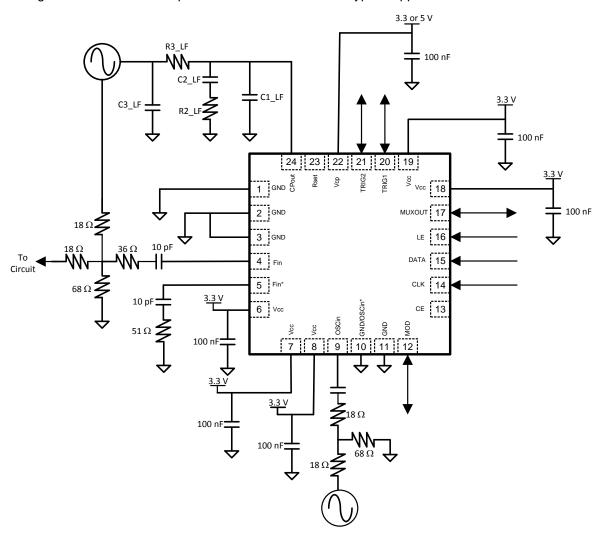

The LMX2492/92-Q1 is a microwave PLL, consisting of a reference input and divider, high frequency input and divider, charge pump, ramp generator, and other digital logic. The Vcc power supply pins run at a nominal 3.3 volts, while the charge pump supply pin, Vcp, operates anywhere from Vcc to 5 volts. The device is designed to operate with an external loop filter and VCO. Modulation is achieved by manipulating the MASH engine.

### 8.2 Functional Block Diagram

### 8.3 Feature Description

### 8.3.1 OSCin Input

The reference can be applied in several ways. If using a differential input, this should be terminated differentially with a 100 ohm resistance and AC coupled to the OSCin and GND/OSCin\* terminals. If driving this single-ended, then the GND/OSCin\* terminal may be grounded, although better performance is attained by connecting the GND/OSCin\* terminal through a series resistance and capacitance to ground to match the OSCin terminal impedance.

#### 8.3.2 OSCin Doubler

The OSCin doubler allows the input signal to the OSCin to be doubled in order to have higher phase detector frequencies. This works by clocking on both the rising and falling edges of the input signal, so it therefore requires a 50% input duty cycle.

### 8.3.3 R Divider

The R counter is 16 bits divides the OSCin signal from 1 to 65535. If DIFF\_R = 0, then any value can be chosen in this range. If DIFF R=1, then the divide is restricted to 2,4,8, and 16, but allows for higher OSCin frequencies.

### 8.3.4 PLL N Divider

The 16 bit N divider divides the signal at the Fin terminal down to the phase detector frequency. It contains a 4/5 prescaler that creates minimum divide restrictions, but allows the N value to increment in values of one.

| Modulator Order                      | Minimum N<br>Divide |

|--------------------------------------|---------------------|

| Integer Mode, 1st<br>Order Modulator | 16                  |

| 2nd Order Modulator                  | 17                  |

| 3rd Order Modulator                  | 19                  |

| 4th Order Modulator                  | 25                  |

ZHCSCB6-MARCH 2014 www.ti.com.cn

#### 8.3.5 Fractional Circuitry

The fractional circuitry controls the N divider with delta sigma modulation that supports a programmable first, second, third, and fourth order modulator. The fractional denominator is a fully programmable 24-bit denominator that can support any value from 1,2,..., 224, with the exception when the device is running one of the ramps, and in this case it is a fixed size of 2<sup>24</sup>.

### 8.3.6 PLL Phase Detector and Charge Pump

The phase detector compares the outputs of the R and N dividers and generates a correction voltage corresponding to the phase error. This voltage is converted to a correction current by the charge pump. The phase detector frequency, f<sub>PD</sub>, can be calculated as follows: f<sub>PD</sub> = f<sub>OSCin</sub> × OSC\_2X / R.

The charge pump supply voltage on this device, Vcp, can be either run at the Vcc voltage, or up to 5.25 volts in order to get higher tuning voltages to present to the VCO.

#### 8.3.7 External Loop Filter

The loop filter is external to the device and is application specific. Texas Instruments website has details on this at www.ti.com.

### 8.3.8 Fastlock and Cycle Slip Reduction

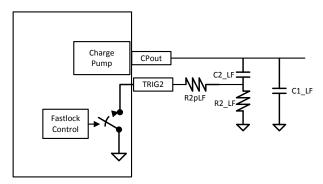

The Fastlock<sup>™</sup> and Cycle Slip Reduction features can be used to improved lock time. When the frequency is changed, a timeout counter can be used to engage these features for a prescribed number of phase detector cycles. During this time that the timeout counter is counting down, the device can be used to pull a terminal from high impedance to ground switch in an extra resistor (R2pLF), change the charge pump current (FL\_CPG), or change the phase detector frequency. TRIG2 is recommended for switching the resistor with a setting of TRIG2\_MUX = Fastlock (2) and TRIG2\_PIN = Inverted/Open Drain (5).

| Parameter                                    | Normal Operation | Fastlock Operation |

|----------------------------------------------|------------------|--------------------|

| Charge Pump Gain                             | CPG              | FL_CPG             |

| Device Pin<br>(TRIG1, TRIG2, MOD, or MUXout) | High Impedance   | Grounded           |

The resistor and the charge pump current are changed simultaneously so that the phase margin remains the same while the loop bandwidth is by a factor of K as shown in the following table:

| Parameter                    | Symbol | Calculation                      |  |  |

|------------------------------|--------|----------------------------------|--|--|

| Charge Pump Gain in Fastlock | FL_CPG | Typically use the highest value. |  |  |

| Loop Bandwidth Multiplier    | К      | K=sqrt(FL_CPG/CPG)               |  |  |

| External Resistor            | R2pLF  | R2 / (K-1)                       |  |  |

ZHCSCB6-MARCH 2014 www.ti.com.cn

Cycle slip reduction is another method that can also be used to speed up lock time by reducing cycle slipping. Cycle slipping typically occurs when the phase detector frequency exceeds about 100x the loop bandwidth of the PLL. Cycle slip reduction works in a different way than fastlock. To use this, the phase detector frequency is decreased while the charge pump current is simultaneously increased by the same factor. Although the loop bandwidth is unchanged, the ratio of the phase detector frequency to the loop bandwidth is, and this is helpful for cases when the phase detector frequency is high. Because cycle slip reduction changes the phase detector rate. it also impacts other things that are based on the phase detector rate, such as the fastlock timeout-counter and ramping controls.

# 8.3.9 Lock Detect and Charge Pump Voltage Monitor

The LMX2492/92-Q1 offers two methods to determine if the PLL is in lock, charge pump voltage monitoring and digital lock detect. These features can be used individually or in conjunction to give a reliable indication of when the PLL is in lock. The output of this detection can be routed to the TRIG1, TRIG2, MOD, or MUXout terminals.

#### 8.3.9.1 Charge Pump Voltage Monitor

The charge pump voltage monitor allows the user to set low (CMP\_THR\_LOW) and high (CMP\_THR\_HIGH) thresholds for a comparator that monitors the charge pump output voltage.

| Vcp   | Threshold                                  | Suggested Level   |

|-------|--------------------------------------------|-------------------|

| 22.7  | CPM_THR_LOW<br>= (Vthresh + 0.08) / 0.085  | 6 for 0.5V limit  |

| 3.3 V | CPM_THR_HIGH<br>= (Vthresh - 0.96) / 0.044 | 42 for 2.8V limit |

| 50.7  | CPM_THR_LOW<br>= (Vthresh + 0.056) / 0.137 | 4 for 0.5V limit  |

| 5.0 V | CPM_THR_HIGH<br>= (Vthresh -1.23) / 0.071  | 46 for 4.5V limit |

#### 8.3.9.2 Digital Lock Detect

Digital lock detect works by comparing the phase error as presented to the phase detector. If the phase error plus the delay as specified by the PFD DLY bit is outside the tolerance as specified by DLD TOL, then this comparison would be considered to be an error, otherwise passing. The DLD\_ERR\_CNT specifies how may errors are necessary to cause the circuit to consider the PLL to be unlocked. The DLD PASS CNT specifies how many passing comparisons are necessary to cause the PLL to be considered to be locked and also resets the count for the errors. The DLD TOL value should be set to no more than half of a phase detector period plus the PFD DLY value. The DLD ERR CNT and DLD PASS CNT values can be decreased to make the circuit more sensitive. If the circuit is too sensitive, then chattering can occur and the DLD ERR CNT. DLD\_PASS\_CNT, or DLD\_TOL values should be increased.

Note that if the OSCin signal goes away and there is no noise or self-oscillation at the OSCin pin, then it is possible for the digital lock detect to indicate a locked state when the PLL really is not in lock. If this is a concern. then digital lock detect can be combined with charge pump voltage monitor to detect this situation...

### 8.3.10 FSK/PSK Modulation

Two level FSK or PSK modulation can be created whenever a trigger event, as defined by the FSK TRIG field is detected. This trigger can be defined as a transition on a terminal (TRIG1, TRIG2, MOD, or MUXout) or done purely in software. The RAMP\_PM\_EN bit defines the modulation to be either FSK or PSK and the FSK\_DEV register determines the amount of the deviation. Remember that the FSK\_DEV[32:0] field is programmed as the 2's complement of the actual desired FSK DEV value. This modulation can be added to the modulation created from the ramping functions as well.

| RAMP_PM_EN | RAMP_PM_EN Modulation Type |                                  |  |  |  |

|------------|----------------------------|----------------------------------|--|--|--|

| 0          | 2 Level FSK                | Fpd x FSK_DEV / 2 <sup>24</sup>  |  |  |  |

| 1          | 2 Level PSK                | 360° × FSK_DEV / 2 <sup>24</sup> |  |  |  |

www.ti.com.cn

### 8.3.11 Ramping Functions

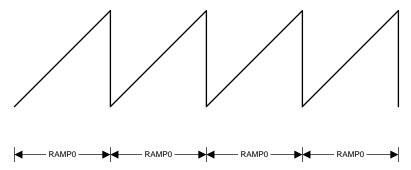

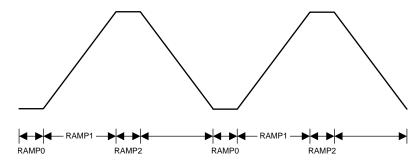

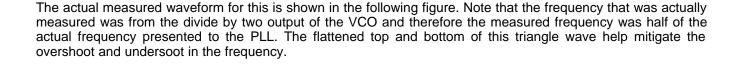

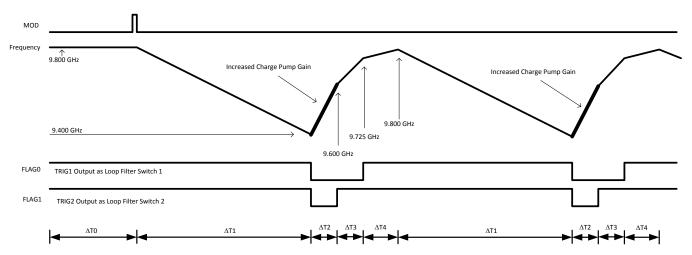

The LMX2492/92-Q1 supports a broad and flexible class of FMCW modulation formed by up to 8 linear ramps. When the ramping function is running, the denominator is fixed to a forced value of  $2^{2^4} = 16777216$ . The waveform always starts at RAMP0 when the LSB of the PLL\_N (R16) is written to. After it is set up, it will start at the initial frequency and have piecewise linear frequency modulation that deviates from this initial frequency as specified by the modulation. Each of the eight ramps can be individually programmed. Various settings are as follows

| Ramp Characteristic   | Programming Field Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ramp Length           | RAMPx_LEN<br>RAMPx_DLY              | The user programs the length of the ramp in phase detector cycles. If RAMPx_DLY=1, then each count of RAMPx_LEN is actually two phase detector cycles.                                                                                                                                                                                                                                                                                                                                             |

| Ramp Slope            | RAMPx_LEN<br>RAMPx_DLY<br>RAMPx_INC | The user does not directly program slope of the line, but rather this is done by defining how long the ramp is and how much the fractional numerator is increased per phase detector cycle. The value for RAMPx_INC is calculated by taking the total expected increase in the frequency, expressed in terms of how much the fractional numerator increases, and dividing it by RAMPx_LEN. The value programmed into RAMPx_INC is actually the two's complement of the desired mathematical value. |

| Trigger for Next Ramp | RAMPx_NEXT_TRIG                     | The event that triggers the next ramp can be defined to be the ramp finishing or can wait for a trigger as defined by TRIG A, TRIG B, or TRIG C.                                                                                                                                                                                                                                                                                                                                                   |

| Next Ramp             | RAMPx_NEXT                          | This sets the ramp that follows. Waveforms are constructed by defining a chain ramp segments. To make the waveform repeat, make RAMPx_NEXT point to the first ramp in the pattern.                                                                                                                                                                                                                                                                                                                 |

| Ramp Fastlock         | RAMPx_FL                            | This allows the ramp to use a different charge pump current or use Fastlock                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Ramp Flags            | RAMPx_FLAG                          | This allows the ramp to set a flag that can be routed to external terminals to trigger other devices.                                                                                                                                                                                                                                                                                                                                                                                              |

### 8.3.11.1 Ramp Count

If it is desired that the ramping waveform keep repeating, then all that is needed is to make the RAMPx\_NEXT of the final ramp equal to the first ramp. This will run until the RAMP\_EN bit is set to zero. If this is not desired, then one can use the RAMP\_COUNT to specify how may times the specified pattern is to repeat.

#### 8.3.11.2 Ramp Comparators and Ramp Limits

The ramp comparators and ramp limits use programable thresholds to allow the device to detect whenever the modulated waveform frequency crosses a limit as set by the user. The difference between these is that comparators set a flag to alert the user while a ramp limits prevent the frequency from going beyond the prescribed threshold. In either case, these thresholds are expressed by programming the Extended\_Fractional\_Numerator.

Extended\_Fractional\_Numerator = Fractional\_Numerator + (N-N\*) > 2<sup>24</sup>

Extended\_Fractional\_Numerator = Fractional\_Numerator +  $(N-N^*)$  x  $2^{2^4}$  In the above, N is the PLL feedback value without ramping and N\* is the instantaneous value during ramping. The actual value programmed is the 2's complement of Extended\_Fractional\_Numerator.

| Туре                | Programming Bit        | Threshold                                                                                                                                                                                                                                                                                 |

|---------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Doma Limita         | RAMP_LIMIT_LOW         | Lower Limit                                                                                                                                                                                                                                                                               |

| Ramp Limits         | RAMP_LIMIT_HIGH        | Upper Limit                                                                                                                                                                                                                                                                               |

| Ramp<br>Comparators | RAMP_CMP0<br>RAMP_CMP1 | For the ramp comparators, if the ramp is increasing and exceeds the value as specified by RAMP_CMPx, then the flag will go high, otherwise it is low. If the ramp is decreasing and goes below the value as specified by RAMP_CMPx, then the flag will go high, otherwise it will be low. |

#### 8.3.12 Power on Reset (POR)

The power on reset circuitry sets all the registers to a default state when the device is powered up. This same reset can be done by programming SWRST=1. In the programming section, the power on reset state is given for all the programmable fields.

ZHCSCB6-MARCH 2014 www.ti.com.cn

#### 8.4 Device Functional Modes

The two primary ways to use the LMX2492/92-Q1 are to run it to generate a set of frequencies

### 8.4.1 Continuous Frequency Generator

In this mode, the LMX2492/92-Q1 generates a single frequency that only changes when the N divider is programmed to a new value. In this mode, the RAMP\_EN bit is set to 0 and the ramping controls are not used. The fractional denominator can be programmed to any value from 1 to 16777216. In this kind of application, the PLL is tuned to different channels, but at each channel, the goal is to generate a stable fixed frequency.

### 8.4.1.1 Integer Mode Operation

In integer mode operation, the VCO frequency needs to be an integer multiple of the phase detector frequency. This can be the case when the output frequency or frequencies are nicely related to the input frequency. As a rule of thumb, if this an be done with a phase detector of as high as the lesser of 10 MHz or the OSCin frequency, then this makes sense. To operate the device in integer mode, disable the fractional circuitry by programming the fractional order (FRAC\_ORDER), dithering (FRAC\_DITH), and numerator (FRAC\_NUM) to zero.

### 8.4.1.2 Fractional Mode Operation

In fractional mode, the output frequency does not need to be an integer multiple of the phase detector frequency. This makes sense when the channel spacing is more narrow or the input and output frequencies are not nicely related. There are several programmable controls for this such as the modulator order, fractional dithering, fractional numerator, and fractional denominator. There are many trade-offs with choosing these, but here are some guidelines

| Parameter                            | Field Name           | How to Choose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fractional Numerator and Denominator | FRAC_NUM<br>FRAC_DEN | The first step is to find the fractional denominator. To do this, find the frequency that divides the phase detector frequency by the channel spacing. For instance, if the output ranges from 5000 to 5050 in 5 MHz steps and the phase detector is 100 MHz, then the fractional denominator is 100 MHz/5 = 20. So for a an output of 5015 MHz, the N divider would be 50 + 3/20. In this case, the fractional numerator is 3 and the fractional denominator is 20. Sometimes when dithering is used, it makes sense to express this as a larger equivalent fraction. Note that if ramping is active, the fractional denominator is forced to $2^{24}$ . |

| Fractional Order                     | FRAC_ORDER           | There are many trade-offs, but in general try either the 2nd or 3rd order modulator as starting points. The 3rd order modulator may give lower main spurs, but may generate others. Also if dithering is involved, it can generate phase noise.                                                                                                                                                                                                                                                                                                                                                                                                           |

| Dithering                            | FRAC_DITH            | Dithering can reduce some fractional spurs, but add noise. Consult application note AN-1879 for more details on this.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### 8.4.2 Modulated Waveform Generator

In this mode, the device can generate a broad class of frequency sweeping waveforms. The user can specify up to 8 linear segments in order to generate these waveforms. When the ramping function is running, the denominator is fixed to a forced value of  $2^{24} = 16777216$

In addition to the ramping functions, there is also the capability to use a terminal to add phase or frequency modulation that can be done by itself or added on top of the waveforms created by the ramp generation functions.

### 8.5 Programming

### 8.5.1 Loading Registers

The device is programmed using several 24 bit registers. The first 16 bits of the register are the address, followed by the next 8 bits of data. The user has the option to pull the LE terminal high after this data, or keep sending data and it will apply this data to the next lower register. So instead of sending three registers of 24 bits each, one could send a single 40 bit register with the 16 bits of address and 24 bits of data. For that matter, the entire device could be programmed as a single register if desired.

### 8.6 Register Map

Registers are programmed in REVERSE order from highest to lowest. Registers NOT shown in this table or marked as reserved can be written as all 0's unless otherwise stated. The POR value is the power on reset value that is assigned when the device is powered up or the SWRST bit is asserted.

Table 1. Register Map

| Reg   | jister    | D7             | D6            | D5                | D4               | D3               | D2             | D1          | D0       | POR  |

|-------|-----------|----------------|---------------|-------------------|------------------|------------------|----------------|-------------|----------|------|

| 0     | 0         | 0              | 0             | 0                 | 1                | 1                | 0              | 0           | 0        | 0x18 |

| 1     | 0x1       |                | 1             | I                 | Rese             | erved            | I              | 1           | •        | 0x00 |

| 2     | 0x2       | 0              | 0             | 0                 | 0                | 0                | SWRST          | POWERD      | OWN[1:0] | 0x00 |

| 3-15  | 0x3 - 0xF |                |               | •                 | Rese             | erved            | •              |             |          | -    |

| 16    | 0x10      |                |               |                   | PLL_I            | N[7:0]           |                |             |          | 0x64 |

| 17    | 0x11      |                |               |                   | PLL_N            | N[15:8]          |                |             |          | 0x00 |

| 18    | 0x12      | 0              | FR            | AC_ORDER[         | 2:0]             | FRAC_DI          | THER[1:0]      | PLL_N       | I[17:16] | 0x00 |

| 19    | 0x13      |                |               |                   | FRAC_N           | IUM[7:0]         |                |             |          | 0x00 |

| 20    | 0x14      |                |               |                   | FRAC_N           | UM[15:8]         |                |             |          | 0x00 |

| 21    | 0x15      |                |               |                   | FRAC_NI          | JM[23:16]        |                |             |          | 0x00 |

| 22    | 0x16      |                |               |                   | FRAC_E           | DEN[7:0]         |                |             |          | 0x00 |

| 23    | 0x17      |                |               |                   | FRAC_D           | EN[15:8]         |                |             |          | 0x00 |

| 24    | 0x18      |                |               |                   | FRAC_DI          | EN[23:16]        |                |             |          | 0x00 |

| 25    | 0x19      |                |               |                   | PLL_I            | R[7:0]           |                |             |          | 0x04 |

| 26    | 0x1A      |                |               |                   | PLL_F            | R[15:8]          |                |             |          | 0x00 |

| 27    | 0x1B      | 0              | FL_CS         | SR[1:0]           | PFD_D            | LY[1:0]          | PLL_R_<br>DIFF | 0           | OSC_2X   | 0x08 |

| 28    | 0x1C      | 0              | 0             | CPPOL             |                  |                  | CPG[4:0]       |             |          | 0x00 |

| 29    | 0x1D      | F              | L_TOC[10:8    | 5]                |                  |                  | FL_CPG[4:0]    |             |          | 0x00 |

| 30    | 0x1E      | 0              | CPM_<br>FLAGL |                   |                  | CPM_THR          | _LOW[5:0]      |             |          | 0x0a |

| 31    | 0x1F      | 0              | CPM_<br>FLAGH |                   |                  | CPM_THR          | _HIGH[5:0]     |             |          | 0x32 |

| 32    | 0x20      |                |               |                   | FL_TC            | C[7:0]           |                |             |          | 0x00 |

| 33    | 0x21      |                |               |                   | DLD_PASS         | S_CNT[7:0]       |                |             |          | 0x0f |

| 34    | 0x22      |                | DLD_TOL[2:0   | )]                |                  | DLD              | _ERR_CNTF      | R[4:0]      |          | 0x00 |

| 35    | 0x23      | MOD_<br>MUX[5] | 1             | MUXout<br>_MUX[5] | TRIG2<br>_MUX[5] | TRIG1<br>_MUX[5] | 0              | 0           | 1        | 0x41 |

| 36    | 0x24      |                | TF            | RIG1_MUX[4        | :0]              |                  | Т              | RIG1_PIN[2: | 0]       | 0x08 |

| 37    | 0x25      |                | TF            | RIG2_MUX[4        | :0]              |                  | Т              | RIG2_PIN[2: | 0]       | 0x10 |

| 38    | 0x26      |                | N             | 1OD_MUX[4:        | 0]               |                  | N              | MOD_PIN[2:0 | 0]       | 0x18 |

| 39    | 0x27      |                | MU            | JXout_MUX[4       | 1:0]             |                  | М              | UXout_PIN[2 | ::0]     | 0x38 |

| 40-57 | 0x28-0x39 |                |               |                   | Rese             | erved            |                |             |          | -    |

www.ti.com.cn

# **Register Map (continued)**

# Table 1. Register Map (continued)

| Re | gister | D7 I                   | D6                                            | D5         | D4             | D3                | D2              | D1                | D0                | POR  |

|----|--------|------------------------|-----------------------------------------------|------------|----------------|-------------------|-----------------|-------------------|-------------------|------|

| 58 | 0x3A   | RA                     | AMP_TR                                        | RIG_A[3:0] | RAMP_<br>PM_EN | RAMP_<br>CLK      | RAMP_EN         | 0x00              |                   |      |

| 59 | 0x3B   | RA                     | AMP_TR                                        | RIG_C[3:0] |                |                   | RAMP_TI         | RIG_B[3:0]        |                   | 0x00 |

| 60 | 0x3C   |                        |                                               |            | RAMP_C         | MP0[7:0]          |                 |                   |                   | 0x00 |

| 61 | 0x3D   |                        |                                               |            | RAMP_C         | MP0[15:8]         |                 |                   |                   | 0x00 |

| 62 | 0x3E   |                        |                                               |            | RAMP_CN        | /IP0[23:16]       |                 |                   |                   | 0x00 |

| 63 | 0x3F   |                        |                                               |            | RAMP_CN        | /IP0[31:24]       |                 |                   |                   | 0x00 |

| 64 | 0x40   |                        |                                               |            | RAMP_CM        | P0_EN[7:0]        |                 |                   |                   | 0x00 |

| 65 | 0x41   |                        |                                               |            | RAMP_C         | MP1[7:0]          |                 |                   |                   | 0x00 |

| 66 | 0x42   |                        |                                               |            | RAMP_C         | MP1[15:8]         |                 |                   |                   | 0x00 |

| 67 | 0x43   |                        |                                               |            | RAMP_CN        | /IP1[23:16]       |                 |                   |                   | 0x00 |

| 68 | 0x44   |                        |                                               |            | RAMP_CN        | /IP1[31:24]       |                 |                   |                   | 0x00 |

| 69 | 0x45   |                        |                                               |            | RAMP_CM        | P1_EN[7:0]        |                 |                   |                   | 0x00 |

| 70 | 0x46   | 0                      | FSK_TRIG[1:0] R.                              |            |                | RAMP_<br>LIML[32] | FSK_<br>DEV[32] | RAMP_<br>CMP1[32] | RAMP_<br>CMP0[32] | 0x08 |

| 71 | 0x47   |                        |                                               |            | FSK_D          | EV[7:0]           |                 |                   |                   | 0x00 |

| 72 | 0x48   |                        |                                               |            | FSK_DI         | EV[15:8]          |                 |                   |                   | 0x00 |

| 73 | 0x49   |                        |                                               |            | FSK_DE         | V[23:16]          |                 |                   |                   | 0x00 |

| 74 | 0x4A   |                        |                                               |            | FSK_DE         | V[31:24]          |                 |                   |                   | 0x00 |

| 75 | 0x4B   |                        |                                               |            | RAMP_LIMI      | T_LOW[7:0]        |                 |                   |                   | 0x00 |

| 76 | 0x4C   |                        |                                               |            | RAMP_LIMI      | Γ_LOW[15:8]       |                 |                   |                   | 0x00 |

| 77 | 0x4D   |                        |                                               |            | RAMP_LIMIT     | _LOW[23:16        | ]               |                   |                   | 0x00 |

| 78 | 0x4E   |                        |                                               |            | RAMP_LIMIT     | _LOW[31:24        | ]               |                   |                   | 0x00 |

| 79 | 0x4F   |                        |                                               |            | RAMP_LIMI      | T_HIGH[7:0]       |                 |                   |                   | 0xff |

| 80 | 0x50   |                        |                                               |            | RAMP_LIMIT     | Γ_HIGH[15:8]      |                 |                   |                   | 0xff |

| 81 | 0x51   | RAMP_LIMIT_HIGH[23:16] |                                               |            |                |                   |                 |                   |                   | 0xff |

| 82 | 0x52   |                        | RAMP_LIMIT_HIGH[31:24]                        |            |                |                   |                 |                   |                   |      |

| 83 | 0x53   |                        | RAMP_COUNT[7:0]                               |            |                |                   |                 |                   |                   |      |

| 84 | 0x54   | RAMP_TRIG_IN           | AMP_TRIG_INC[1:0] RAMP_ AUTO RAMP_COUNT[12:8] |            |                |                   |                 |                   |                   |      |

| 85 | 0x55   |                        | <u></u>                                       |            | Reserved       |                   |                 |                   |                   |      |

www.ti.com.cn

# **Register Map (continued)**

# Table 1. Register Map (continued)

| Reg | gister | D7            | D6              | D5                                     | D4             | D3                 | B D2 D1 D0    |         |           | POR  |  |

|-----|--------|---------------|-----------------|----------------------------------------|----------------|--------------------|---------------|---------|-----------|------|--|

| 86  | 0x56   |               |                 |                                        | RAMP0_INC[7:0] |                    |               |         |           |      |  |

| 87  | 0x57   |               | RAMP0_INC[15:8] |                                        |                |                    |               |         |           |      |  |

| 88  | 0x58   |               |                 |                                        | RAMP0_         | NC[23:16]          |               |         |           | 0x00 |  |

| 89  | 0x59   | RAMP0_<br>DLY | RAMP0_<br>FL    |                                        |                | RAMP0_I            | NC[29:24]     |         |           | 0x00 |  |

| 90  | 0x5A   |               |                 |                                        | RAMP0_         | _LEN[7:0]          |               |         |           | 0x00 |  |

| 91  | 0x5B   |               |                 |                                        | RAMP0_         | LEN[15:8]          |               |         |           | 0x00 |  |

| 92  | 0x5C   | RA            | MP0_NEXT[2      | 2:0]                                   | RAM<br>NEXT_1  | ИР0_<br>TRIG[1:0]  | RAMP0_<br>RST | RAMP0_I | FLAG[1:0] | 0x00 |  |

| 93  | 0x5D   |               |                 |                                        | RAMP1          | _INC[7:0]          |               |         |           | 0x00 |  |

| 94  | 0x5E   |               |                 |                                        | RAMP1_         | INC[15:8]          |               |         |           | 0x00 |  |

| 95  | 0x5F   |               |                 |                                        | RAMP1_         | NC[23:16]          |               |         |           | 0x00 |  |

| 96  | 0x60   | RAMP1_<br>DLY | RAMP1_<br>FL    |                                        |                | RAMP1_I            | NC[29:24]     |         |           | 0x00 |  |

| 97  | 0x61   |               |                 |                                        | RAMP1_         | _LEN[7:0]          |               |         |           | 0x00 |  |

| 98  | 0x62   |               |                 |                                        | RAMP1_         | LEN[15:8]          |               |         |           | 0x00 |  |

| 99  | 0x63   | RA            | MP1_NEXT[2      | EXT[2:0] RAMP1_ RAMP1_ RAMP1_FLAG[1:0] |                |                    |               | 0x00    |           |      |  |

| 100 | 0x64   |               |                 |                                        | RAMP2          | _INC[7:0]          | •             | •       |           | 0x00 |  |

| 101 | 0x65   |               |                 |                                        | RAMP2_         | INC[15:8]          |               |         |           | 0x00 |  |

| 102 | 0x66   |               |                 |                                        | RAMP2_         | NC[23:16]          |               |         |           | 0x00 |  |

| 103 | 0x67   | RAMP2<br>DLY  | RAMP2_<br>FL    |                                        |                | RAMP2_I            | NC[29:24]     |         |           | 0x00 |  |

| 104 | 0x68   |               | I               | I                                      | RAMP2_         | _LEN[7:0]          |               |         |           | 0x00 |  |

| 105 | 0x69   |               |                 |                                        | RAMP2_         | LEN[15:8]          |               |         |           | 0x00 |  |

| 106 | 0x6A   | RA            | MP2_NEXT[2      | 2:0]                                   |                | //P2_<br>TRIG[1:0] | RAMP2_<br>RST | RAMP2_I | FLAG[1:0] | 0x00 |  |

| 107 | 0x6B   |               |                 |                                        | RAMP3          | _INC[7:0]          | "             | I.      |           | 0x00 |  |

| 108 | 0x6C   |               |                 |                                        | RAMP3_         | INC[15:8]          |               |         |           | 0x00 |  |

| 109 | 0x6D   |               |                 |                                        | RAMP3_         | NC[23:16]          |               |         |           | 0x00 |  |

| 110 | 0x6E   | RAMP3_<br>DLY | RAMP3_<br>FL    | RAMP3_INC[29:24]                       |                |                    |               |         | 0x00      |      |  |

| 111 | 0x6F   |               | ı               | ı                                      | RAMP3_         | _LEN[7:0]          |               |         |           | 0x00 |  |

| 112 | 0x70   |               |                 |                                        | RAMP3_         | LEN[15:8]          |               |         |           | 0x00 |  |

| 113 | 0x71   | RA            | MP3_NEXT[2      | 2:0]                                   |                | //P3_<br>TRIG[1:0] | RAMP3_<br>RST | RAMP3_I | FLAG[1:0] | 0x00 |  |

ZHCSCB6-MARCH 2014 www.ti.com.cn

# **Register Map (continued)**

# Table 1. Register Map (continued)

| Regi      | ster            | D7            | D6              | D5   | D4            | D3                 | D2            | D1     | D0        | POR  |

|-----------|-----------------|---------------|-----------------|------|---------------|--------------------|---------------|--------|-----------|------|

| 114       | 0x72            |               |                 |      | RAMP4         | _INC[7:0]          |               |        |           | 0x00 |

| 115       | 0x73            |               | RAMP4_INC[15:8] |      |               |                    |               |        |           |      |

| 116       | 0x74            |               |                 |      | RAMP4_        | NC[23:16]          |               |        |           | 0x00 |

| 117       | 0x75            | RAMP4_<br>DLY | RAMP4_<br>FL    |      |               | RAMP4_             | INC[29:24]    |        |           | 0x00 |

| 118       | 0x76            |               |                 |      | RAMP4_        | _LEN[7:0]          |               |        |           | 0x00 |

| 119       | 0x77            |               |                 |      | RAMP4_        | LEN[15:8]          |               |        |           | 0x00 |

| 120       | 0x78            | RA            | MP4_NEXT[       | 2:0] |               | /IP4_<br>TRIG[1:0] | RAMP4_<br>RST | RAMP4_ | FLAG[1:0] | 0x00 |

| 121       | 0x79            |               |                 |      | RAMP5         | _INC[7:0]          |               |        |           | 0x00 |

| 122       | 0x7A            |               |                 |      | RAMP5_        | INC[15:8]          |               |        |           | 0x00 |

| 123       | 0x7B            |               |                 |      | RAMP5_        | NC[23:16]          |               |        |           | 0x00 |

| 124       | 0x7C            | RAMP5_<br>DLY | RAMP5_<br>FL    |      |               | RAMP5_             | INC[29:24]    |        |           | 0x00 |

| 125       | 0x7D            |               | I.              |      | RAMP5_        | _LEN[7:0]          |               |        |           | 0x00 |

| 126       | 0x7E            |               |                 |      | RAMP5_        | LEN[15:8]          |               |        |           | 0x00 |

| 127       | 0x7F            | RA            | RAMP5_NEXT[2:0] |      |               |                    |               |        | FLAG[1:0] | 0x00 |

| 128       | 0x80            |               |                 |      | RAMP6         | _INC[7:0]          |               |        |           | 0x00 |

| 129       | 0x81            |               |                 |      | RAMP6_        | INC[15:8]          |               |        |           | 0x00 |

| 130       | 0x82            |               |                 |      | RAMP6_        | NC[23:16]          |               |        |           | 0x00 |

| 131       | 0x83            | RAMP6_<br>DLY | RAMP6_<br>FL    |      |               | RAMP6_             | INC[29:24]    |        |           | 0x00 |

| 132       | 0x84            |               |                 |      | RAMP6_        | _LEN[7:0]          |               |        |           | 0x00 |

| 133       | 0x85            |               |                 |      | RAMP6_        | LEN[15:8]          |               |        |           | 0x00 |

| 134       | 0x86            | RA            | MP6_NEXT[       | 2:0] | RAN<br>NEXT_1 | /IP6_<br>TRIG[1:0] | RAMP6_<br>RST | RAMP6_ | FLAG[1:0] | 0x00 |

| 135       | 0x87            |               |                 |      | RAMP7         | _INC[7:0]          |               |        |           | 0x00 |

| 136       | 0x88            |               |                 |      | RAMP7_        | INC[15:8]          |               |        |           | 0x00 |

| 137       | 0x89            |               |                 |      | RAMP7_        | NC[23:16]          |               |        |           | 0x00 |

| 138       | 0x8A            | RAMP7_<br>DLY | RAMP7_<br>FL    |      |               | RAMP7_             | INC[29:24]    |        |           | 0x00 |

| 139       | 0x8B            |               | ı               | ı    | RAMP7_        | _LEN[7:0]          |               |        |           | 0x00 |

| 140       | 0x8C            |               |                 |      | RAMP7_        | LEN[15:8]          |               |        |           | 0x00 |

| 141       | 0x8D            | RA            | MP7_NEXT[       | 2:0] | DAMD7 DAMD7   |                    |               |        |           | 0x00 |

| 142-32767 | 0x8E-<br>0x7fff |               |                 |      | Res           | erved              |               |        |           | 0x00 |

# 8.7 Register Field Descriptions

The following sections go through all the programmable fields and their states. Additional information is also available in the applications and feature descriptions sections as well. The POR column is the power on reset state that this field assumes if not programmed.

### 8.7.1 POWERDOWN and Reset Fields

### **Table 2. POWERDOWN and Reset Fields**

| Field     | Location | POR | Description and States                                                           |       |                                          |             |  |  |

|-----------|----------|-----|----------------------------------------------------------------------------------|-------|------------------------------------------|-------------|--|--|

|           |          |     |                                                                                  | Value | POWERDOWN State                          |             |  |  |

|           |          |     | POWERDOWN Control                                                                | 0     | POWERDOWN, ignore CE                     |             |  |  |

| POWERDOWN | R2[1:0]  | 0   |                                                                                  | 1     | Power Up, ignore CE                      |             |  |  |

| [1:0]     |          |     |                                                                                  | 2     | Power State Defined by CE terminal state |             |  |  |

|           |          |     |                                                                                  | 3     | Reserved                                 |             |  |  |

|           | R2[2]    | 0   |                                                                                  |       | Value                                    | Reset State |  |  |

| SWRST     |          |     | Software Reset. Setting this bit sets all registers to their POR default values. | 0     | Normal Operation                         |             |  |  |

|           |          |     | registers to their r Ork default values.                                         | 1     | Register Reset                           |             |  |  |

www.ti.com.cn

### 8.7.2 Dividers and Fractional Controls

# **Table 3. Dividers and Fractional Controls**

| Field                | Location            | POR | Description and States                                                                                                         |              |                               |

|----------------------|---------------------|-----|--------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------|

| PLL_N<br>[17:0]      | R18[1] to<br>R16[0] | 16  | Feedback N counter Divide value. Minimum the register R16 begins any ramp execution                                            |              |                               |

|                      |                     |     |                                                                                                                                | Value        | Dither                        |

|                      |                     |     |                                                                                                                                | 0            | Weak                          |

| FRAC_ DITHER [1:0]   | R18[3:2]            | 0   | Dither used by the fractional modulator                                                                                        | 1            | Medium                        |

| [1.0]                |                     |     |                                                                                                                                | 2            | Strong                        |

|                      |                     |     |                                                                                                                                | 3            | Disabled                      |

|                      |                     |     |                                                                                                                                | Value        | Modulator Order               |

|                      |                     |     |                                                                                                                                | 0            | Integer Mode                  |

|                      |                     |     |                                                                                                                                | 1            | 1st Order Modulator           |

| FRAC_ ORDER<br>[2:0] | R18[6:4]            | 0   | Fractional Modulator order                                                                                                     | 2            | 2nd Order Modulator           |

| [2.0]                |                     |     |                                                                                                                                | 3            | 3rd Order Modulator           |

|                      |                     |     |                                                                                                                                | 4            | 4th Order Modulator           |

|                      |                     |     |                                                                                                                                | 5-7          | Reserved                      |

| FRAC_NUM<br>[23:0]   | R21[7] to<br>R19[0] | 0   | Fractional Numerator. This value should denominator.                                                                           | be less that | an or equal to the fractional |

| FRAC_DEN<br>[23:0]   | R24[7] to<br>R22[0] | 0   | Fractional Denominator. If the RAMP_EN=1, this field is ignored and the denominator is fixed to $2^{24}$ .                     |              |                               |

| PLL_R<br>[15:0]      | R26[7] to<br>R25[0] | 1   | Reference Divider value. Selecting 1 will bypass counter.                                                                      |              |                               |

|                      | R27[0]              | 0   | Enables the Doubler before the Reference divider                                                                               | Value        | Doubler                       |

| OSC_2X               |                     |     |                                                                                                                                | 0            | Disabled                      |

|                      |                     |     | dividei                                                                                                                        | 1            | Enabled                       |

|                      |                     |     | Enables the Differential R counter.<br>This allows for higher OSCin frequencies,<br>but restricts PLL_R to divides of 2,4,8 or | Value        | R Divider                     |

| PLL_R _DIFF          | R27[2]              | 0   |                                                                                                                                | 0            | Single-Ended                  |