# UCC21710-Q1 Single Channel Isolated Gate Driver for SiC/IGBT with Advanced Protection and High-CMTI

## 1 Features

- · Single channel SiC/IGBT isolated gate driver

- AEC-Q100 qualified for automotive applications (qualification planned)

- SiC MOSFETs and IGBTs up to 1700 V

- 33-V maximum output drive voltage (VDD-COM)

- Split outputs with ±10-A peak drive current

- 150-V/ns min. CMTI

- OC sense IGBT/SiC overcurrent

- Response time 200 ns

- Active miller clamp

- 4-A internal active miller clamp

- Soft turn-off when fault happen

- Soft turn-off 400 mA

- Isolated analog sensor with PWM output for

- Temperature sense with NTC or thermal diode

- High voltage DC-link or phase voltage

- Alarm FLT on over current and reset from RST/EN

- Fast enable/disable response on RST/EN

- Reject noise transient and pulse on input pins

- UVLO with power good on RDY

- VDD UVLO 12 V

- Inputs/outputs with over/under-shoot immunity

- Small propagation delay and pulse/part skew

- Operating temperature range –40°C to 125°C

- Safety-related certifications (planned):

- 8000-V<sub>PK</sub> V<sub>IOTM</sub> and 2121-V<sub>PK</sub> V<sub>IORM</sub>

Reinforced Isolation per DIN V VDE V 0884-11

(VDE V 0884-11): 2017-01

- 5700-V<sub>RMS</sub> Isolation for 1 Minute per UL1577

# 2 Applications

- · Traction Inverter for EVs

- On-board charger and dc charging station

- Industrial motor drives

- Server, telecom, and industrial power supplies

- Uninterruptible power supplies (UPS)

# 3 Description

The UCC21710-Q1 is a galvanic isolated single channel gate drivers designed for up to 1700V SiC MOSFETs and IGBTs with advanced protection features, best-in-class dynamic performance and robustness. UCC21710-Q1 has up to ±10-A peak source and sink current.

The input side is isolated from the output side with SiO<sub>2</sub> capacitive isolation technology, supporting up to 1.5-kV<sub>RMS</sub> working voltage, 12.8-kV<sub>PK</sub> surge immunity with longer than 40 years Isolation barrier life, as well as providing low part-to-part skew, >150V/ns common mode noise immunity (CMTI).

The UCC21710-Q1 includes the state-of-art protection features, such as fast overcurrent and short circuit detection, shunt current sensing support, fault reporting, active miller clamp, input and output side power supply UVLO to optimize SiC and IGBT switching behavior and robustness. The isolated analog to PWM sensor can be utilized for easier temperature or voltage sensing, further increasing the drivers' versatility and simplifying the system design effort, size and cost.

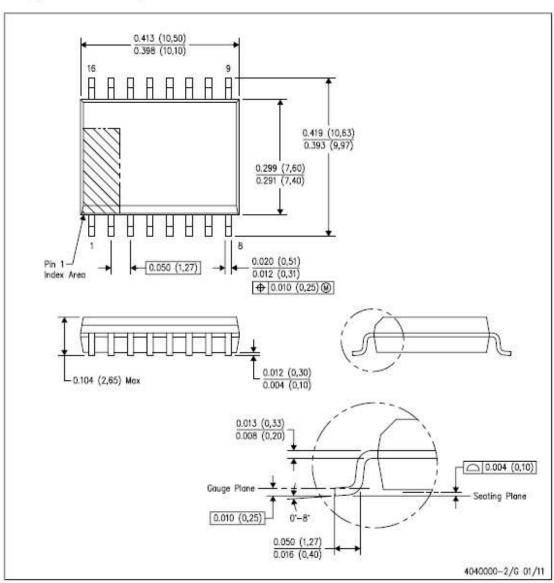

Table 1. Device Information(1)

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)  |

|-------------|------------|------------------|

| UCC21710-Q1 | DW SOIC-16 | 10.3 mm × 7.5 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

# **Table of Contents**

| 1 | Features 1                           |    | 7.5 OC (Over Current) Protection                    | 17    |

|---|--------------------------------------|----|-----------------------------------------------------|-------|

| 2 | Applications 1                       | 8  | Detailed Description                                | 18    |

| 3 | Description 1                        |    | 8.1 Overview                                        | 18    |

| 4 | Revision History2                    |    | 8.2 Functional Block Diagram                        | 18    |

| 5 | Pin Configuration and Functions      |    | 8.3 Feature Description                             | 19    |

| 6 | Specifications                       |    | 8.4 Device Functional Modes                         | 26    |

| 0 | 6.1 Absolute Maximum Ratings         | 9  | Applications and Implementation                     | 27    |

|   | 6.2 ESD Ratings                      |    | 9.1 Application Information                         | 27    |

|   | 6.3 Recommended Operating Conditions |    | 9.2 Typical Application                             | 27    |

|   | 6.4 Thermal Information              | 10 | Power Supply Recommendations                        | 32    |

|   | 6.5 Power Ratings                    | 11 | Layout                                              |       |

|   | 6.6 Insulation Specifications        |    | 11.1 Layout Guidelines                              |       |

|   | 6.7 Safety-Related Certifications    |    | 11.2 Layout Example                                 |       |

|   | 6.8 Safety Limiting Values 8         | 12 | Device and Documentation Support                    | 35    |

|   | 6.9 Electrical Characteristics9      |    | 12.1 Documentation Support                          | 35    |

|   | 6.10 Switching Characteristics       |    | 12.2 Receiving Notification of Documentation Update | es 35 |

| 7 | Parameter Measurement Information 11 |    | 12.3 Community Resource                             | 35    |

| - | 7.1 Propagation Delay                |    | 12.4 Trademarks                                     | 35    |

|   | 7.2 Input Deglitch Filter            |    | 12.5 Electrostatic Discharge Caution                | 35    |

|   | 7.3 Active Miller Clamp              |    | 12.6 Glossary                                       |       |

|   | 7.4 Under Voltage Lockout (UVLO)     | 13 | Mechanical, Packaging, and Orderable Information    |       |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Original (January 2019) to Revision A

Page

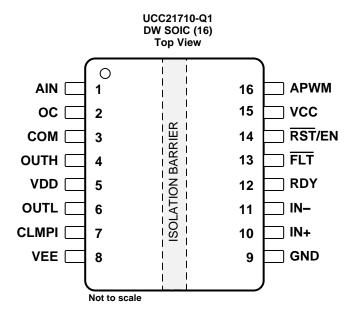

# 5 Pin Configuration and Functions

# **Pin Functions**

| PIN    |     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|-----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | 1/0(1)             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AIN    | 1   | I                  | Isolated analog sensing input, parallel a small capacitor to COM for better noise immunity                                                                                                                                                                                                                                                                                                                                                                                                                              |

| OC     | 2   | I                  | Over current detection pin, support lower threshold for SenseFET and Shunt resistor sensing                                                                                                                                                                                                                                                                                                                                                                                                                             |

| COM    | 3   | Р                  | Common ground reference, connecting to emitter pin for IGBT and source pin for SiC-MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OUTH   | 4   | 0                  | Gate driver output pull up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VDD    | 5   | Р                  | Positive supply rail for gate drive voltage, Bypassing a >5.1µF capacitor to COM to support specified gate driver source peak current capability                                                                                                                                                                                                                                                                                                                                                                        |

| OUTL   | 6   | 0                  | Gate driver output pull down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CLMPI  | 7   | I                  | Internal Active miller clamp, connecting this pin directly to the gate of the power transistor                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VEE    | 8   | Р                  | Negative supply rail for gate drive voltage. Bypassing a >5.1µF capacitor to COM to support specified gate driver sink peak current capability                                                                                                                                                                                                                                                                                                                                                                          |

| GND    | 9   | Р                  | Input power supply and logic ground reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| IN+    | 10  | I                  | Non-inverting gate driver control input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IN-    | 11  | I                  | Inverting gate driver control input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RDY    | 12  | 0                  | Power good for VCC-GND, VDD-COM and COM-VEE                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FLT    | 13  | 0                  | Active low fault alarm output upon over current or short circuit. FLT is in open drain configuration and can be paralleled with other faults.                                                                                                                                                                                                                                                                                                                                                                           |

| RST/EN | 14  | I                  | The RST/EN serves two purposes:  1) Enable / shutdown of the output side. The FET is turned off by a general turn-off, if terminal EN is set to low;  2) Resets the OC condition signaled on FLT pin. if terminal RST/EN is set to low for more than 800ns. A reset of signal FLT is asserted at the rising edge of terminal RST/EN.  For automatic RESET function, this pin only serves as an EN pin. Enable / shutdown of the output side. The FET is turned off by a general turn-off, if terminal EN is set to low. |

| VCC    | 15  | Р                  | Input power supply from 3V to 5.5V, bypassing a >100nF capacitor to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| APWM   | 16  | 0                  | Isolated Analog Sensing PWM output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

(1) P = Power, G = Ground, I = Input, O = Output

Submit Documentation Feedback

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                     | PARAMETER                                                          |                                            | MIN     | MAX     | UNIT |

|-------------------------------------|--------------------------------------------------------------------|--------------------------------------------|---------|---------|------|

| VCC                                 | VCC – GND                                                          |                                            | -0.3    | 6       | V    |

| VDD                                 | VDD – COM                                                          |                                            | -0.3    | 36      | V    |

| VEE                                 | VEE – COM                                                          |                                            | -17.5   | 0.3     | V    |

| V <sub>MAX</sub>                    | VDD – VEE                                                          |                                            | -0.3    | 36      | V    |

| N. N. 707/FN                        |                                                                    | DC                                         | GND-0.3 | VCC     | V    |

| IN+, IN-, RST/EN                    |                                                                    | Transient, less than 100 ns <sup>(2)</sup> | GND-5.0 | VCC+5.0 | V    |

| AIN                                 | Reference to COM                                                   |                                            | -0.3    | 5       | V    |

| OC                                  | Reference to COM                                                   |                                            | -0.3    | 6       |      |

| OUTU OUTU OLMDI                     |                                                                    | DC                                         | VEE-0.3 | VDD     | V    |

| OUTH, OUTL , CLMPI                  |                                                                    | Transient, less than 100 ns <sup>(2)</sup> | VEE-5.0 | VDD+5.0 | V    |

| RDY, FLT, APWM                      |                                                                    |                                            | GND-0.3 | VCC     | V    |

| I <sub>FLT</sub> , I <sub>RDY</sub> | I <sub>FLT</sub> , I <sub>RDY</sub> FLT, and RDY pin input current |                                            |         | 20      | mA   |

| APWM APWM pin output current        |                                                                    |                                            | 20      | mA      |      |

| T <sub>J</sub>                      | Junction temperature range                                         |                                            | -40     | 150     | °C   |

| T <sub>stg</sub>                    | Storage temperature range                                          |                                            | -65     | 150     | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                                                                                     | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> Due to complexity, there may be risk for 4kV. 2.5kV is a conservative spec. | ±2500 | V    |

|                    |                         | Charged-device model (CDM), per AEC Q100-011                                                                                        | ±1500 |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 6.3 Recommended Operating Conditions

| PARAMETER           |                                          |                          | MIN     | MAX     | UNIT |

|---------------------|------------------------------------------|--------------------------|---------|---------|------|

| VCC                 | VCC-GND                                  | VCC-GND                  |         |         | V    |

| VDD                 | VDD-COM                                  |                          | 13      | 33      | V    |

| $V_{MAX}$           | VDD-VEE                                  |                          | _       | 33      | V    |

| IN+, IN-, RST/EN    | Reference to GND                         | High level input voltage | 0.7×VCC | VCC     | V    |

| IN+, IN-, KSI/EN    |                                          | Low level input voltage  | 0       | 0.3×VCC |      |

| AIN                 | Reference to COM                         |                          | 0.5     | 4.5     | V    |

| t <sub>RST/EN</sub> | Minimum pulse width that reset the fault |                          | 800     |         | ns   |

| T <sub>A</sub>      | Ambient Temperature                      |                          | -40     | 125     | °C   |

| $T_J$               | Junction temperatur                      | e                        | -40     | 150     | °C   |

<sup>(2)</sup> Values are verified by characterization on bench.

# 6.4 Thermal Information

|                      | THERMAL METRIC <sup>(1)</sup>                | DW (SOIC) | UNIT |

|----------------------|----------------------------------------------|-----------|------|

|                      |                                              | 16        |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 68.3      | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 27.5      | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 10.9      | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 14.1      | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 10.3      | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Power Ratings

| PARAMETER       |                                               | TEST CONDITIONS                                                                   | Value | UNIT |

|-----------------|-----------------------------------------------|-----------------------------------------------------------------------------------|-------|------|

| $P_{D}$         | Maximum power dissipation (both sides)        |                                                                                   | 985   | mW   |

| P <sub>D1</sub> | Maximum power dissipation by transmitter side | VCC=5V, VDD-COM=20V, COM-VEE=5V,<br>IN+/=5V, 150kHz, 50% Duty cycle for 10nF load | 20    | mW   |

| P <sub>D2</sub> | Maximum power dissipation by receiver side    | 1117 = 51, 100ki iz, 5576 Bally dyele for 1011 lead                               | 965   | mW   |

Submit Documentation Feedback

# 6.6 Insulation Specifications

|                   | PARAMETER                                          | TEST CONDITIONS                                                                                                                                                                        | VALUE              | UNIT             |

|-------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|

| GENERA            | L                                                  |                                                                                                                                                                                        |                    |                  |

| CLR               | External clearance <sup>(1)</sup>                  | Shortest terminal-to-terminal distance through air                                                                                                                                     | > 8                | mm               |

| CPG               | External creepage <sup>(1)</sup>                   | Shortest terminal-to-terminal distance across the package surface                                                                                                                      | > 8                | mm               |

| DTI               | Distance through the insulation                    | Minimum internal gap (Internal clearance) of the double insulation (2 × 0.0085 mm)                                                                                                     | > 17               | μm               |

| CTI               | Comparative tracking index                         | DIN EN 60112 (VDE 0303-11); IEC 60112                                                                                                                                                  | > 600              | V                |

|                   | Material group                                     | According to IEC 60664–1                                                                                                                                                               | I                  |                  |

|                   |                                                    | Rated mains voltage ≤ 300 V <sub>RMS</sub>                                                                                                                                             | I-IV               |                  |

|                   | Overvoltage Category per IEC 60664-1               | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                                                                                                                             | I-IV               |                  |

|                   |                                                    | Rated mains voltage ≤ 1000 V <sub>RMS</sub>                                                                                                                                            | I-III              |                  |

| DIN V VD          | E V 0884-11 (VDE V 0884-11):2017-01 <sup>(2)</sup> | -                                                                                                                                                                                      |                    |                  |

| $V_{IORM}$        | Maximum repetitive peak isolation voltage          | AC voltage (bipolar)                                                                                                                                                                   | 2121               | $V_{PK}$         |

| $V_{IOWM}$        | Maximum isolation working voltage                  | AC voltage (sine wave) Time dependent dielectric breakdown (TDDB) test                                                                                                                 | 1500               | V <sub>RMS</sub> |

| · IOWIVI          |                                                    | DC voltage                                                                                                                                                                             | 2121               | $V_{DC}$         |

| .,                |                                                    | V <sub>TEST</sub> =V <sub>IOTM</sub> , t = 60 s (qualification test)                                                                                                                   | 8000               |                  |

| $V_{IOTM}$        | Maximum transient isolation voltage                | V <sub>TEST</sub> =1.2 x V <sub>IOTM</sub> , t = 1 s (100% production test)                                                                                                            | 9600               | V <sub>PK</sub>  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage (3)                | Test method per IEC 62368-1, 1.2/50 µs waveform, V <sub>TEST</sub> = 1.6 × V <sub>IOSM</sub> = 12800 V <sub>PK</sub> (qualification)                                                   | 8000               | V <sub>PK</sub>  |

|                   | Apparent charge <sup>(4)</sup>                     | Method a: After I/O safety test subgroup 2/3, $V_{ini}$ = $V_{IOTM}$ , $t_{ini}$ = 60 s; $V_{pd(m)}$ = 1.2 × $V_{IORM}$ = 2545 $V_{PK}$ , $t_m$ = 10 s                                 | ≤ 5                |                  |

| $q_{pd}$          |                                                    | Method a: After environmental tests subgroup 1, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60$ s; $V_{pd(m)} = 1.6 \times V_{IORM} = 3394$ $V_{PK}$ , $t_m = 10$ s                              | ≤ 5                | pC               |

|                   |                                                    | Method b1: At routine test (100% production) and preconditioning (type test) $V_{ini} = V_{IOTM}$ , $t_{ini} = 1$ s; $V_{pd(m)} = 1.875 \times V_{IORM} = 3977 \ V_{PK}$ , $t_m = 1$ s | ≤ 5                |                  |

| C <sub>IO</sub>   | Barrier capacitance, input to output (5)           | $V_{IO} = 0.5 \sin (2\pi ft), f = 1 \text{ MHz}$                                                                                                                                       | ~ 1                | pF               |

|                   |                                                    | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25°C                                                                                                                                         | ≥ 10 <sup>12</sup> |                  |

| R <sub>IO</sub>   | Insulation resistance, input to output (5)         | V <sub>IO</sub> = 500 V, 100°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                                                | ≥ 10 <sup>11</sup> | Ω                |

|                   |                                                    | V <sub>IO</sub> = 500 V at T <sub>S</sub> = 150°C                                                                                                                                      | ≥ 10 <sup>9</sup>  |                  |

|                   | Pollution degree                                   |                                                                                                                                                                                        | 2                  |                  |

|                   | Climatic category                                  |                                                                                                                                                                                        | 40/125/21          |                  |

| UL 1577           |                                                    |                                                                                                                                                                                        |                    |                  |

| V <sub>ISO</sub>  | Withstand isolation voltage                        | $V_{TEST}$ = $V_{ISO}$ = 5700 $V_{RMS}$ , t = 60 s (qualification);<br>$V_{TEST}$ = 1.2 × $V_{ISO}$ = 6840 $V_{RMS}$ , t = 1 s (100% production)                                       | 5700               | V <sub>RMS</sub> |

<sup>(1)</sup> Apply creepage and clearance requirements according to the specific equipment isolation standards of an application. Care must be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed circuit board (PCB) do not reduce this distance. Creepage and clearance on a PCB become equal in certain cases. Techniques such as inserting grooves and ribs on the PCB are used to help increase these specifications.

- (3) Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

- (4) Apparent charge is electrical discharge caused by a partial discharge (pd).

- (5) All pins on each side of the barrier tied together creating a two-terminal device

#### 6.7 Safety-Related Certifications

| •                                                                                                                |                                                                    |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| VDE                                                                                                              | UL                                                                 |

| Plan to certify according to DIN V VDE V 0884-11 (VDE V 0884-11):2017-01;<br>DIN EN 61010-1 (VDE 0411-1):2011-07 | Plan to certify according to UL 1577 Component Recognition Program |

<sup>(2)</sup> This coupler is suitable for safe electrical insulation only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

# Safety-Related Certifications (continued)

| VDE                                                                                                                                                                                  | UL                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Reinforced insulation Maximum transient isolation voltage, 8000 $V_{PK}$ ; Maximum repetitive peak isolation voltage, 2121 $V_{PK}$ ; Maximum surge isolation voltage, 8000 $V_{PK}$ | Single protection, 5700 V <sub>RMS</sub> |

| Certification Planned                                                                                                                                                                | Certification Planned                    |

# 6.8 Safety Limiting Values

Safety limiting (1) intends to minimize potential damage to the isolation barrier upon failure of input or output circuitry. A failure of the I/O can allow low resistance to ground or the supply and, without current limiting, dissipate sufficient power to overheat the die and damage the isolation barrier, potentially leading to secondary system failures.

|                | PARAMETER                            | TEST CONDITIONS                                                                           | MIN | TYP | MAX | UNIT |  |

|----------------|--------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|--|

| I <sub>S</sub> | Safety input, output, or supply      | $R_{\theta JA}$ =68.3°C/W, $V_{DD}$ = 20V, $V_{EE}$ =-5V, $T_{J}$ = 150°C, $T_{A}$ = 25°C |     |     | TBD | ^    |  |

|                | current                              | $R_{\theta JA}$ =68.3°C/W, $V_{DD}$ = 20V, $V_{EE}$ =-5V, $T_{J}$ = 150°C, $T_{A}$ = 25°C |     |     | TBD | mA   |  |

| P <sub>S</sub> | Safety input, output, or total power | $R_{\theta JA}$ =68.3°C/W, $V_{DD}$ = 20V, $V_{EE}$ =-5V, $T_{J}$ = 150°C, $T_{A}$ = 25°C |     |     | TBD | mW   |  |

| T <sub>S</sub> | Safety temperature                   |                                                                                           |     |     | 150 | °C   |  |

The safety-limiting constraint is the maximum junction temperature specified in the data sheet. The power dissipation and junction-to-air thermal impedance of the device installed in the application hardware determines the junction temperature. The assumed junction-to-air thermal resistance in the Thermal Information table is that of a device installed on a high-K test board for leaded surface-mount packages. The power is the recommended maximum input voltage times the current. The junction temperature is then the ambient temperature plus the power times the junction-to-air thermal resistance.

## 6.9 Electrical Characteristics

VCC=3.3V or 5.0V, 1uF capacitor from VCC to GND, VDD–COM=20V, 18V or 15V, COM–VEE =0V, 5V, 8V or 15V,  $C_L=100pF$ ,  $-40^{\circ}C<T_J<150^{\circ}C$  (unless otherwise noted)<sup>(1)(2)</sup>.

|                                      | PARAMETER                                             | TEST CONDITIONS                               | MIN  | TYP  | MAX  | UNIT |  |

|--------------------------------------|-------------------------------------------------------|-----------------------------------------------|------|------|------|------|--|

| VCC UVLO THRESI                      | HOLD AND DELAY                                        |                                               |      |      | •    |      |  |

| V <sub>VCC_ON</sub>                  |                                                       |                                               | 2.55 | 2.7  | 2.85 |      |  |

| V <sub>VCC_OFF</sub>                 | VCC-GND                                               |                                               | 2.35 | 2.5  | 2.65 | V    |  |

| V <sub>VCC_HYS</sub>                 |                                                       |                                               |      | 0.2  |      |      |  |

| t <sub>VCCFIL</sub>                  | VCC UVLO Deglitch time                                |                                               |      | 10   |      |      |  |

| t <sub>VCC+ to OUT</sub>             | VCC UVLO on delay to output high                      |                                               |      | 37.8 |      |      |  |

| t <sub>VCC- to</sub> OUT             | VCC UVLO off delay to output                          | IN+ = VCC, IN- = GND                          |      | 10   |      |      |  |

| t <sub>VCC+ to RDY</sub>             | VCC UVLO on delay to RDY high                         |                                               |      | 37.8 |      | μs   |  |

| t <sub>VCC- to RDY</sub>             | VCC UVLO off delay to RDY low                         | RST/EN = VCC                                  |      | 10   |      |      |  |

| VDD UVLO THRESI                      |                                                       | <u> </u>                                      |      |      |      |      |  |

| V <sub>VDD_ON</sub>                  |                                                       |                                               | 11.2 | 12.0 | 12.8 |      |  |

| V <sub>VDD OFF</sub>                 | VDD-COM                                               |                                               | 9.9  | 10.7 | 11.5 | V    |  |

| V <sub>VDD_HYS</sub>                 |                                                       |                                               | 0.0  | 0.8  |      | ·    |  |

| t <sub>VDDFIL</sub>                  | VDD UVLO Deglitch time                                |                                               |      | 5    |      |      |  |

| t <sub>VDD+ to OUT</sub>             | VDD UVLO on delay to output high                      |                                               |      | 5    |      |      |  |

| t <sub>VDD- to OUT</sub>             | VDD UVLO off delay to output low                      | IN+ = VCC, IN- = GND                          |      | 5    |      | μs   |  |

| t <sub>VDD+ to RDY</sub>             | VDD UVLO on delay to RDY high                         |                                               |      | 10   |      | ·    |  |

| t <sub>VDD- to RDY</sub>             | VDD UVLO off delay to RDY low                         | RST/EN = FLT=High                             | 10   |      |      |      |  |

| VCC, VDD QUIESCI                     | ENT CURRENT                                           |                                               |      |      |      |      |  |

|                                      |                                                       | OUT(H) = High, f <sub>S</sub> = 0Hz, AIN=2V   |      | 3    |      |      |  |

| I <sub>VCCQ</sub>                    | VCC quiescent current                                 | OUT(L) = Low, f <sub>S</sub> = 0Hz, AIN=2V    |      |      | mA   |      |  |

|                                      | \/DD :                                                | OUT(H) = High, f <sub>S</sub> = 0Hz, AIN=2V   |      | 4    |      |      |  |

| I <sub>VDDQ</sub>                    | VDD quiescent current                                 | OUT(L) = Low, f <sub>S</sub> = 0Hz, AIN=2V    |      | 3.7  |      | mA   |  |

| LOGIC INPUTS — I                     | N+, IN– and RST/EN                                    |                                               |      |      |      |      |  |

| V <sub>INH</sub>                     | Input high threshold                                  | V <sub>CC</sub> =3.3V                         |      | 1.85 | 2.31 | V    |  |

| V <sub>INL</sub>                     | Input low threshold                                   | V <sub>CC</sub> =3.3V                         | 0.99 | 1.52 |      | V    |  |

| V <sub>INHYS</sub>                   | Input threshold hysteresis                            | V <sub>CC</sub> =3.3V                         |      | 0.33 |      | V    |  |

| I <sub>IH</sub>                      | Input high level input leakage current                | V <sub>IN</sub> = VCC                         |      | 90   |      | μΑ   |  |

| I <sub>IL</sub>                      | Input low level input leakage                         | V <sub>IN</sub> = GND                         |      | -90  |      | μA   |  |

| R <sub>IND</sub>                     | Input pins pull down resistance                       | see Detailed Description for more information |      | 55   |      |      |  |

| R <sub>INU</sub>                     | Input pins pull up resistance                         | see Detailed Description for more information |      | 55   |      | kΩ   |  |

| T <sub>INFIL</sub>                   | IN+, IN– and RST/EN deglitch (ON and OFF) filter time | f <sub>S</sub> = 50kHz                        | 28   | 40   |      | ns   |  |

| T <sub>RSTFIL</sub>                  | Deglitch filter time to reset /FLT                    |                                               | 500  | 650  | 800  | ns   |  |

| GATE DRIVER STA                      | \GE                                                   |                                               | •    |      |      |      |  |

| I <sub>OUT</sub> , I <sub>OUTH</sub> | Peak source current                                   | 0.040                                         |      | -10  |      | Α    |  |

| I <sub>OUT</sub> , I <sub>OUTL</sub> | Peak sink current                                     | C <sub>L</sub> =0.18μF, f <sub>S</sub> =1kHz  |      | 10   |      | Α    |  |

| R <sub>OUTH</sub> <sup>(3)</sup>     | Output pull-up resistance                             | I <sub>OUT</sub> = -0.1A                      |      | 2.5  |      | Ω    |  |

| R <sub>OUTL</sub>                    | Output pull-down resistance                           | I <sub>OUT</sub> = 0.1A                       |      | 0.3  |      | Ω    |  |

| -                                    |                                                       | 1                                             | 1    |      |      |      |  |

- (1) Current are positive into and negative out of the specified terminal.

- (2) All voltages are referenced to COM unless otherwise notified.

- (3) For internal PMOS only. Refer to Feature Description for effective pull-up resistance.

# **Electrical Characteristics (continued)**

VCC=3.3V or 5.0V, 1uF capacitor from VCC to GND, VDD–COM=20V, 18V or 15V, COM–VEE =0V, 5V, 8V or 15V,  $C_i = 100pF$ .  $-40^{\circ}C < T_i < 150^{\circ}C$  (unless otherwise noted)<sup>(1)(2)</sup>.

|                         | PARAMETER                                   | TEST CONDITIONS                                                                             | MIN  | TYP       | MAX      | UNIT |

|-------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------|------|-----------|----------|------|

| V <sub>OUTH</sub>       | High level output voltage                   | I <sub>OUT</sub> = -0.2A, V <sub>DD</sub> =15V                                              |      | 14.5      |          | V    |

| V <sub>OUTL</sub>       | Low level output voltage                    | I <sub>OUT</sub> = 0.2A                                                                     |      | 60        |          | mV   |

| ACTIVE PULLDOV          | VN                                          |                                                                                             |      |           |          |      |

| V <sub>OUTPD</sub>      | Output active pull down on OUT, OUTL        | I <sub>OUTL</sub> or I <sub>OUT</sub> = 0.1×I <sub>OUT(L)(tpy)</sub> ,<br>VDD=OPEN, VEE=COM |      |           | 2.5      | V    |

| INTERNAL ACTIVI         | E MILLER CLAMP                              |                                                                                             |      |           |          |      |

| V <sub>CLMPTH</sub>     | Miller clamp threshold voltage              | Reference to VEE                                                                            | 1.7  | 2.0       | 2.3      | V    |

| V <sub>CLMPI</sub>      | Output low clamp voltage                    | I <sub>CLMPI</sub> = 1A                                                                     |      | VEE + 0.5 |          | V    |

| I <sub>CLMPI</sub>      | Output low clamp current                    | $V_{CLMPI} = 0V$ , $VEE = -2.5V$                                                            |      | 4         |          | Α    |

| R <sub>CLMPI</sub>      | Miller clamp pull down resistance           | I <sub>CLMPI</sub> = 0.2A                                                                   |      | 0.6       |          | Ω    |

| t <sub>DCLMPI</sub>     | Miller clamp ON delay time                  | C <sub>L</sub> = 1.8nF                                                                      |      | 25        | 50       | ns   |

| SHORT CIRCUIT O         | CLAMPING                                    |                                                                                             |      |           |          |      |

| V <sub>CLP-OUT(H)</sub> | $V_{OUT}$ VDD, $V_{OUTH}$ VDD               | OUT = Low, $I_{OUT(H)} = 500$ mA, $t_{CLP} = 10$ us                                         |      | 0.9       |          | V    |

| V <sub>CLP-OUT(L)</sub> | $V_{OUT}$ – $VDD$ , $V_{OUTL}$ – $VDD$      | OUT = High, I <sub>OUT(L)</sub> = 500mA, t <sub>CLP</sub> =10us                             |      | 1.8       |          | V    |

| V <sub>CLP-CLMPI</sub>  | V <sub>CLMPI</sub> -VDD                     | OUT = High, I <sub>CLMPI</sub> = -20mA, t <sub>CLP</sub> =10us                              |      | 1.0       |          | V    |

| OC PROTECTION           |                                             |                                                                                             |      |           |          |      |

| I <sub>DCHG</sub>       | OC pull down current when                   | V <sub>OC</sub> = 1V                                                                        |      | 40        |          | mA   |

| V <sub>OCTH</sub>       | Detection Threshold                         |                                                                                             | 0.63 | 0.7       | 0.77     | V    |

| V <sub>OCL</sub>        | Voltage when OUT(L) = LOW, Reference to COM | I <sub>OC</sub> = 5mA                                                                       |      | 0.13      |          | ٧    |

| t <sub>OCFIL</sub>      | OC fault deglitch filter                    |                                                                                             |      | 150       |          | ns   |

| t <sub>OCOFF</sub>      | OC propagation delay to OUT(L) 90%          |                                                                                             |      | 200       |          | ns   |

| t <sub>OCFLT</sub>      | OC to FLT low delay                         |                                                                                             |      | 600       |          | ns   |

| INTERNAL SOFT           | TURN-OFF                                    |                                                                                             |      |           |          |      |

| I <sub>STO</sub>        | Soft turn-off current on fault conditions   |                                                                                             |      | 400       |          | mA   |

| ISOLATED TEMPE          | ERATURE SENSE AND MONITOR (AIN-             | -APWM)                                                                                      |      |           |          |      |

| V <sub>AIN</sub>        | Analog sensing voltage range                |                                                                                             | 0.5  |           | 4.5      | V    |

| I <sub>AIN</sub>        | Internal current source                     | V <sub>AIN</sub> =2.5V, -40°C< T <sub>J</sub> < 150°C                                       | 196  | 200       | 206      | μΑ   |

| f <sub>APWM</sub>       | APWM output frequency                       | V <sub>AIN</sub> =2.5V                                                                      | 360  | 400       | 440      | kHz  |

| BW <sub>AIN</sub>       | AIN-APWM bandwidth                          |                                                                                             |      | 10        |          | kHz  |

|                         |                                             | V <sub>AIN</sub> = 0.5V                                                                     | 85   | 90        | 95       |      |

| D <sub>APWM</sub>       | APWM Dutycycle                              | V <sub>AIN</sub> = 2.5V                                                                     | 45   | 50        | 55       | %    |

|                         |                                             | V <sub>AIN</sub> = 4.5V                                                                     | 5    | 10        | 15       |      |

| FLT AND RDY REI         | PORTING                                     |                                                                                             |      |           | T.       |      |

| t <sub>RDYHLD</sub>     | VDD UVLO RDY low minimum holding time       |                                                                                             | 0.55 |           | 1        | ms   |

| t <sub>FLTMUTE</sub>    | Output mute time on fault                   | Reset fault through RST/EN                                                                  | 0.55 |           | 1        | ms   |

| R <sub>ODON</sub>       | Open drain output on resistance             | I <sub>ODON</sub> = 5mA                                                                     |      | 30        |          | Ω    |

| V <sub>ODL</sub>        | Open drain low output voltage               | IODON = 5mA                                                                                 |      |           | 0.3      | V    |

| COMMON MODE 1           | FRANSIENT IMMUNITY                          |                                                                                             |      |           | <u> </u> |      |

| СМТІ                    | Common-mode transient immunity              |                                                                                             | 150  |           |          | V/ns |

|                         |                                             | 1                                                                                           |      |           |          |      |

Submit Documentation Feedback

# 6.10 Switching Characteristics

VCC=5.0V, 1uF capacitor from VCC to GND, VDD–COM=20V, 18V or 15V, COM–VEE = 3V, 5V or 8V,  $C_L$ =100pF,

-40°C<T<sub>.</sub><150°C (unless otherwise noted)

|                    | PARAMETER                               | TEST CONDITIONS                     | MIN | TYP | MAX | UNIT |

|--------------------|-----------------------------------------|-------------------------------------|-----|-----|-----|------|

| t <sub>PDHL</sub>  | Propagation delay time –<br>High to Low |                                     |     | 90  |     |      |

| t <sub>PDLH</sub>  | Propagation delay time –<br>Low to High |                                     |     | 90  |     |      |

| PWD                | Pulse width distortion   tpDHL - tpDLH  |                                     |     |     | 25  | ns   |

| t <sub>sk-pp</sub> | Part to Part skew                       | Rising or Falling Propagation Delay |     |     | 30  |      |

| t <sub>r</sub>     | Driver output rise time                 | C <sub>L</sub> =10nF                |     |     | 28  |      |

| t <sub>f</sub>     | Driver output fall time                 | C <sub>L</sub> =10nF                |     |     | 24  |      |

| f <sub>MAX</sub>   | Maximum switching frequency             |                                     |     |     | 1   | MHz  |

# 7 Parameter Measurement Information

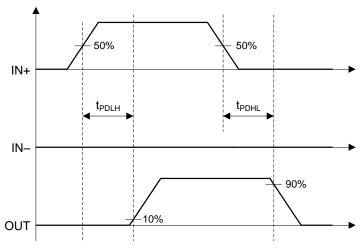

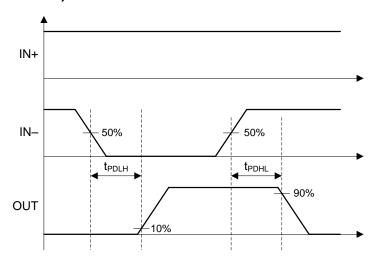

# 7.1 Propagation Delay

# 7.1.1 Regular Turn-OFF

Figure 1 shows the propagation delay measurement for non-inverting configurations. Figure 2 shows the propagation delay measurement with the inverting configurations.

Figure 1. Non-inverting Logic Propagation Delay Measurement

# **Propagation Delay (continued)**

Figure 2. Inverting Logic Propagation Delay Measurement

Submit Documentation Feedback

# 7.2 Input Deglitch Filter

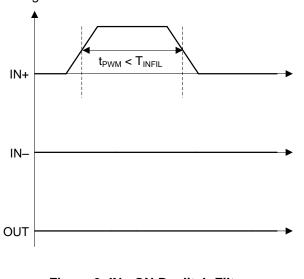

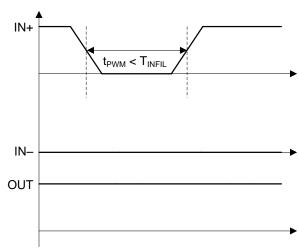

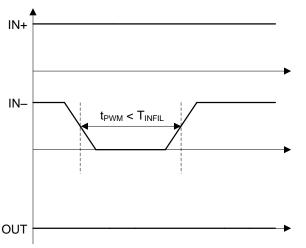

In order to increase the robustness of gate driver over noise transient and accidental small pulses on the input pins, i.e. IN+, IN-, RST/EN, a small deglitch filter was designed to filter out these small transients and make sure there is no faulty output responses or accidental driver malfunctions. When the IN+ or IN- PWM pulse is smaller than the input deglitch filter width, T<sub>INFIL</sub>, there will be no responses on OUT drive signal. Figure 3 and Figure 4 shows the IN+ pin ON and OFF pulse deglitch filter effect. Figure 5 and Figure 6 shows the IN- pin ON and OFF pulse deglitch filter effect.

Figure 3. IN+ ON Deglitch Filter

IN+  $t_{PWM} < T_{INFIL}$ IN-OUT

Figure 4. IN+ OFF Deglitch Filter

Figure 5. IN- ON Deglitch Filter

Figure 6. IN- OFF Deglitch Filter

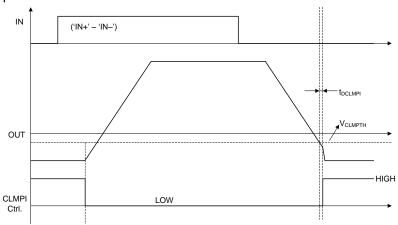

## 7.3 Active Miller Clamp

# 7.3.1 Internal On-chip Active Miller Clamp

For gate driver application with unipolar bias supply or bipolar supply with small negative turn-off voltage, active miller clamp can help add a additional low impedance path to bypass the miller current and prevent the high dV/dt introduced unintentional turn-on through the miller capacitance. Figure 7 shows the timing diagram for on-chip internal miller clamp function.

Figure 7. Timing Diagram for Internal Active Miller Clamp Function

Submit Documentation Feedback

# 7.4 Under Voltage Lockout (UVLO)

UVLO is one of the key protection features designed to protect the system in case of bias supply failures on VCC — primary side power supply, and VDD — secondary side power supply.

#### **7.4.1 VCC UVLO**

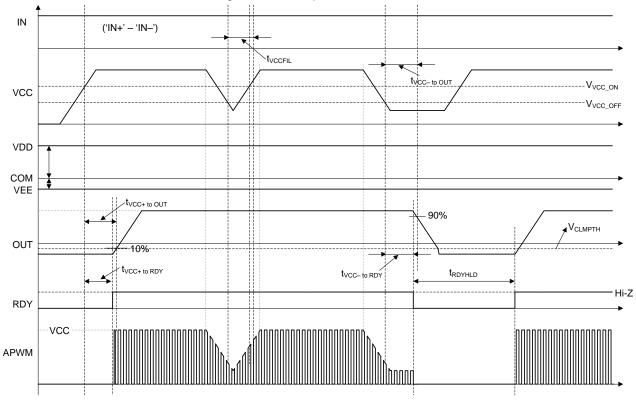

The VCC UVLO protection details are discussed in this section. Figure 8 shows the timing diagram illustrating the definition of UVLO ON/OFF threshold, deglitch filter, response time, RDY and AIN-APWM.

Figure 8. VCC UVLO Protection Timing Diagram

Submit Documentation Feedback

Product Folder Links: UCC21710-Q1

# **Under Voltage Lockout (UVLO) (continued)**

# 7.4.2 VDD UVLO

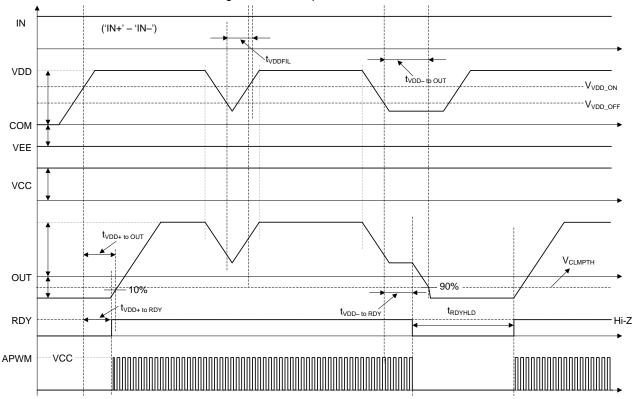

The VDD UVLO protection details are discussed in this section. Figure 9 shows the timing diagram illustrating the definition of UVLO ON/OFF threshold, deglitch filter, response time, RDY and AIN–APWM.

Figure 9. VDD UVLO Protection Timing Diagram

16

Submit Documentation Feedback

Product Folder Links: UCC21710-Q1

# 7.5 OC (Over Current) Protection

## 7.5.1 OC Protection with Soft Turn-OFF

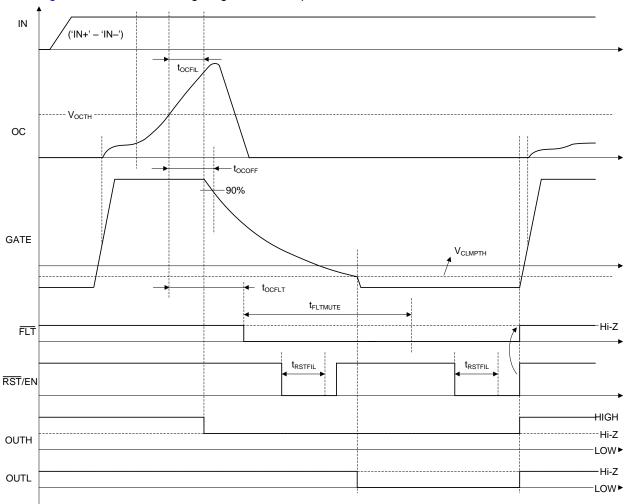

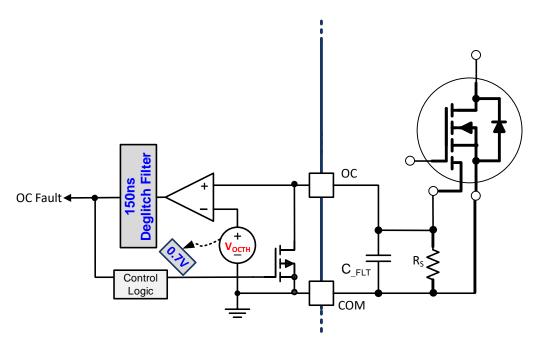

OC Protection is used to sense the current of SiC-MOSFETs and IGBTs under over current or shoot-through condition. Figure 10 shows the timing diagram of OC operation with soft turn-off.

Figure 10. OC Protection with Soft Turn-OFF

# 8 Detailed Description

#### 8.1 Overview

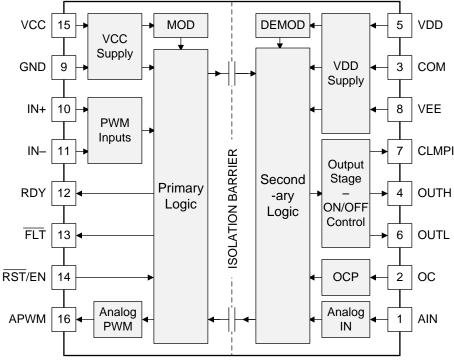

The UCC21710-Q1 device is an advanced isolated gate driver with state-of-art protection and sensing features for SiC MOSFETs and IGBTs. The device can support up 1700V SiC MOSFETs and IGBTs, targeting larger than 10kW applications such as HEV/EV traction inverter, motor drive, on-board and off-board battery charger, solar inverter etc. The galvanic isolation is implemented by the capacitive isolation technology, which can realize a reliable reinforced isolation between the low voltage DSP/MCU and high voltage side.

The  $\pm 10$ A peak sink and source current of UCC21710-Q1 can drive the SiC MOSFET modules and IGBT modules directly without an extra buffer. The input side is isolated with the output side with a reinforced isolation barrier based on capacitive isolation technology. The device can support up to 1.5-kV<sub>RMS</sub> working voltage, 12.8-kV<sub>PK</sub> surge immunity with longer than 40 years isolation barrier life. The minimum 150V/ns CMTI guarantees the reliability of the strong drive strength. The small propagation delay and part-to-part skew can minimize the deadtime setting, so the conduction loss can be reduced.

The device includes extensive protection and monitor features to increase the reliability and robustness of the SiC MOSFET and IGBT based systems. The 12V output side power supply UVLO is suitable for switches with gate voltage ≥ 15V. The active miller clamp feature prevents the false turn on causing by miller capacitance. The device has the state-of-art 200ns overcurrent and short circuit detection time, and fault reporting function to the low voltage side DSP/MCU. The soft turn off is triggered when the overcurrent and short circuit fault is detected, minimizing the short circuit energy while reducing the overshoot voltage on the switches.

The isolated analog to PWM sensor can be used as switch temperature sensing, DC bus voltage sensing, auxiliary power supply sensing, etc. The PWM signal can be fed directly to DSP/MCU or through a low-pass-filter as an analog signal.

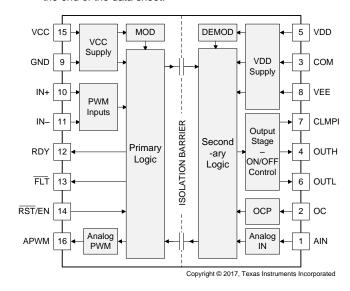

# 8.2 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

Submit Documentation Feedback

## 8.3 Feature Description

# 8.3.1 Power Supply

The input side power supply VCC can support a wide voltage range between 3V and 5.5V. The device supports both unipolar and bipolar power supply on the output side, with a wide range from 13V to 33V. The negative power supply with respect to device source or emitter is usually adopted to avoid false turn on when the other switch in the phase leg is turned on. For IGBTs, the typical value of VDD is 15V, and the VEE is -15V or -8V; for SiC MOSFET, the typical values of VDD is 20V or 18V, and the VEE is -5V, all with respect to the device source, emitter or COM. The negative voltage is especially important for SiC MOSFET due to its fast switching speed.

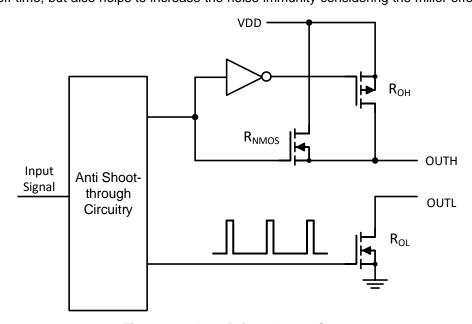

#### 8.3.2 Driver Stage

UCC21710-Q1 has ±10A peak drive strength and is suitable for high power applications. The high drive strength can drive a SiC MOSFET module, IGBT module or paralleled discrete devices directly without extra buffer stage. Regardless of the values of VDD, the peak sink and source current can be kept at 10A. The driver features an important safety function wherein, when the input pins are in floating condition, the OUTH/OUTL is held in LOW state. The split output of the driver stage is depicted in . The driver has rail-to-rail output by implementing a hybrid pull-up structure with a P-Channel MOSFET in parallel with an N-Channel MOSFET, and an N-Channel MOSFET to pulldown. The hybrid pull-up structure delivers the highest peak-source current when it is most needed, during the miller plateau region of the power semiconductor turn-on transient. The ROH in Electrical Table represents the on-resistance of the pull-up P-Channel MOSFET. However, the effective pull-up resistance is much smaller than ROH. Since the pull-up N-Channel MOSFET has much smaller on-resistance than the P-Channel MOSFET, the pull-up N-Channel MOSFET dominates most of the turn-on transient, until the voltage on OUTH pin is about 3V below VDD voltage. The effective resistance of the hybrid pull-up structure during this period is about 2 x R<sub>OL</sub> for UCC21710-Q1. The P-Channel MOSFET is then taking in charge to pull up the OUTH voltage to VDD rail. The low pull-up impedance results in strong drive strength during the turn-on transient, which shortens the charging time of the input capacitance of the power semiconductor and reduces the turn on switching loss.

The pull-down structure of the driver stage is implemented solely by a pull-down N-Channel MOSFET. The on-resistance of the N-Channel MOSFET  $R_{OL}$  can be found in the Electrical Table. This MOSFET can ensure the OUTL voltage be pulled down to VEE rail. The low pull-down impedance not only results in high sink current to reduce the turn-off time, but also helps to increase the noise immunity considering the miller effect.

Figure 11. Gate Driver Output Stage

#### 8.3.3 VCC and VDD Undervoltage Lockout (UVLO)

UCC21710-Q1 implements the internal UVLO protection feature for both input and output power supplies VCC and VDD. When the supply voltage is lower than the threshold voltage, the driver output is held as LOW. The output only goes HIGH when both VCC and VDD are out of the UVLO status. The UVLO protection feature not only reduces the power consumption of the driver itself during low power supply voltage condition, but also increases the efficiency of the power stage. For SiC MOSFET and IGBT, the on-resistance reduces while the gate-source voltage or gate-emitter voltage increases. If the power semiconductor is turned on with a low VDD value, the conduction loss increases significantly and can lead to a thermal issue and efficiency reduction of the power stage. The typical VDD value of IGBT is 15V, and the typical VDD value of SiC MOSFET is 18V or 20V. UCC21710-Q1 implements 12V threshold voltage of VDD UVLO, with 800mV hysteresis; -3V threshold voltage of VEE UVLO, with 400mV hysteresis. This threshold voltage is suitable for both SiC MOSFET and IGBT.

The UVLO protection block features with hysteresis and deglitch filter, which help to improve the noise immunity of the power supply. During the turn on and turn off switching transient, the driver sources and sinks a peak transient current from the power supply, which can result in sudden voltage drop of the power supply. With hysteresis and UVLO deglitch filter, the internal UVLO protection block will ignore small noises during the normal switching transients.

The timing diagrams of the UVLO feature of VCC and VDD are shown in Figure 8, and Figure 9. The RDY pin on the input side is used to indicate the power good condition. The RDY pin is open drain. During UVLO condition, the RDY pin is held in low status and connected to GND. Normally the pin is pulled up externally to VCC to indicate the power good. The AIN-APWM function stops working during the UVLO status. The APWM pin on the input side will be held LOW.

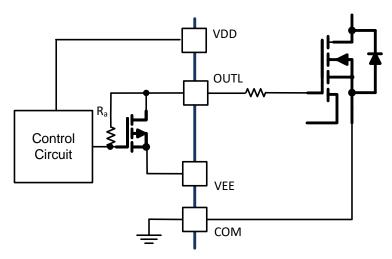

## 8.3.4 Active Pulldown

UCC21710-Q1 implements an active pulldown feature to ensure the OUTH/OUTL pin clamping to VEE when the VDD is open. The OUTH/OUTL pin is in high-impedance status when VDD is open, the active pulldown feature can prevent the output be false turned on before the device is back to control.

Figure 12. Active Pulldown

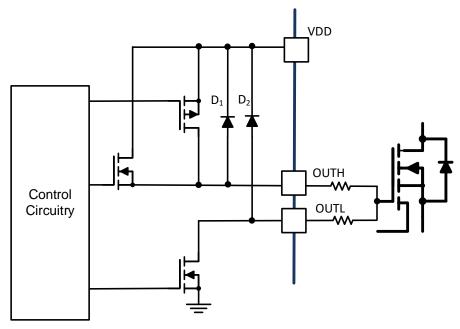

# 8.3.5 Short Circuit Clamping

During short circuit condition, the miller capacitance can cause a current sinking to the OUTH/OUTL pin due to the high dV/dt and boost the OUTH/OUTL voltage. The short circuit clamping feature of UCC21710-Q1 can clamp the OUTH/OUTL pin voltage to be slightly higher than VDD, which can protect the power semiconductors from a gate-source and gate-emitter overvoltage breakdown. This feature is realized by an internal diode from the OUTH/OUTL to VDD.

Submit Documentation Feedback

Figure 13. Short Circuit Clamping

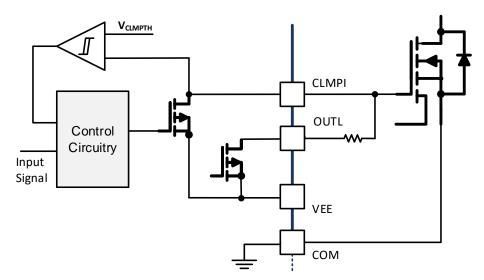

#### 8.3.6 Active Miller Clamp

Active miller clamp feature is important to prevent the false turn-on while the driver is in OFF state. In applications which the device can be in synchronous rectifier mode, the body diode conducts the current during the deadtime while the device is in OFF state, the drain-source or collector-emitter voltage remains the same and the dV/dt happens when the other power semiconductor of the phase leg turns on. The low internal pull-down impedance of UCC21710-Q1 can provide a strong pulldown to hold the OUTL to VEE. However, external gate resistance is usually adopted to limit the dV/dt. The miller effect during the turn on transient of the other power semiconductor can cause a voltage drop on the external gate resistor, which boost the gate-source or gateemitter voltage. If the voltage on V<sub>GS</sub> or V<sub>GE</sub> is higher than the threshold voltage of the power semiconductor, a shoot through can happen and cause catastrophic damage. The active miller clamp feature is implemented in UCC21710-Q1, which bypasses the gate resistor and directly senses the gate voltage. The internal pulldown FET is triggered when the gate voltage is lower than V<sub>CI MPTH</sub>, which is 2V above VEE, and creates a low impedance path to avoid the false turn on issue.

Product Folder Links: UCC21710-Q1

Figure 14. Active Miller Clamp

#### 8.3.7 Overcurrent and Short Circuit Protection

The UCC21710-Q1 implements a fast overcurrent and short circuit protection feature to protect the SiC MOSFET or IGBT from catastrophic breakdown during fault. The OC pin of the device has a typical 0.7V threshold with respect to COM, source or emitter of the power semiconductor. When the input is in floating condition, or the output is held in low state, the OC pin is pulled down by an internal MOSFET and held in LOW state, which prevents the overcurrent and short circuit fault from false triggering. The OC pin is in high-impedance state when the output is in high state, which means the overcurrent and short circuit protection feature only works when the power semiconductor is in on state. The internal pulldown MOSFET helps to discharge the voltage of OC pin when the power semiconductor is turned off.

The overcurrent and short circuit protection feature should preferably be pairing with a split source SiC MOSFET module or split emitter IGBT module. The current mirror in the split leg of the power semiconductor can scale down the drain current or collector current. The current can be accurately measured by a precision sense resistor. If the voltage of the sensed resistor higher than the overcurrent threshold  $V_{\text{OCTH}}$  is detected, the soft turn-off is initiated. A fault will be reported to the input side to DSP/MCU. The output is held to LOW after the fault is detected, and can only be reset by the RST/EN pin. The state-of-art overcurrent and short circuit detection time helps to ensure a short shutdown time for SiC MOSFET and IGBT.

Except for pairing with the split source SiC MOSFET or split emitter IGBT module, the short circuit protection feature can also be paired with DESAT circuit by modifying the circuit and scaling down the voltage. The DESAT threshold can be programmable in this case, which increases the versatility of the device. Caution must be excised when the OC pin is driven by a shunt resistor which is in series in the power switching loop.

- High current and high dl/dt during the overcurrent and short circuit fault can cause a voltage bounce on shunt resistor's parasitic inductance and board layout parasitic, which results in false trigger of OC pin. High precision, low ESL and small value resistor must be used in this approach.

- Shunt resistor approach is not recommended for high power applications and short circuit protection of the low power applications.

The detailed applications of the overcurrent and short circuit feature will be discussed in the Application and Implementation section.

Figure 15. Overcurrent and Short Circuit Protection

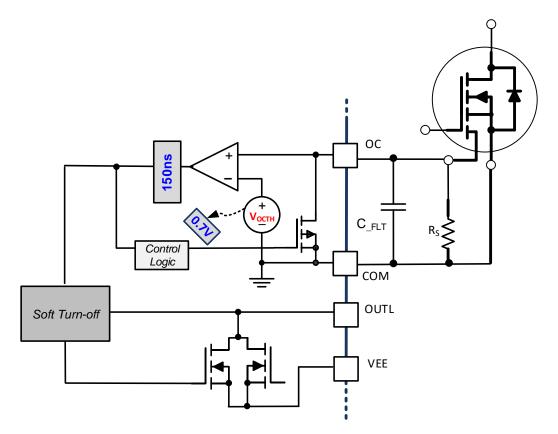

#### 8.3.8 Soft Turn-off

UCC21710-Q1 initiates a soft turn-off when the overcurrent and short circuit protection is triggered. When the overcurrent and short circuit fault happens, the power semiconductor transits from the linear region to the saturation region very fast. The channel current is controlled by the gate voltage and decreasing in a soft manner, thus the overshoot of the power semiconductor is limited and prevents the overvoltage breakdown. There is a tradeoff between the overshoot voltage and short circuit energy. The turn off speed needs to be slow to limit the overshoot voltage, but the shutdown time should not be too long that the large energy dissipation can breakdown the device. The 400mA soft turn off current of UCC21710-Q1 makes sure the power switches is safely turned off during short circuit events. The timing diagram of soft turn-off shows in Figure 10.

Figure 16. Soft Turn-off

# 8.3.9 Fault (FLT, Reset and Enable (RST/EN)

The  $\overline{\text{FLT}}$  pin of UCC21710-Q1 is open drain and can report a fault signal to the DSP/MCU when the overcurrent and short circuit fault is detected through OC pin. The  $\overline{\text{FLT}}$  pin is pulled down to GND, and is held in low state unless a reset signal is received from  $\overline{\text{RST/EN}}$ . The device has a fault mute time  $t_{\text{FLTMUTE}}$ , within which the device ignores any reset signal.

The  $\overline{RST}/EN$  is pulled down internally. The device is disabled by default if the  $\overline{RST}/EN$  pin is floating. The pin has two purposes:

- Resets the overcurrent and short circuit fault signaled on FLT pin. The RST/EN pin is active low, if the pin is set and held in low state for more than t<sub>RSTFIL</sub>, the fault signal is reset andFLT is reset back to the high impedance status at the rising edge of RST/EN pin.

- Enable and shutdown the device. If the RST/EN pin is pulled low, the driver is disabled and shut down by the

regular turn off. The pin must be pulled up externally to enable the part, otherwise the device is disabled by

default.

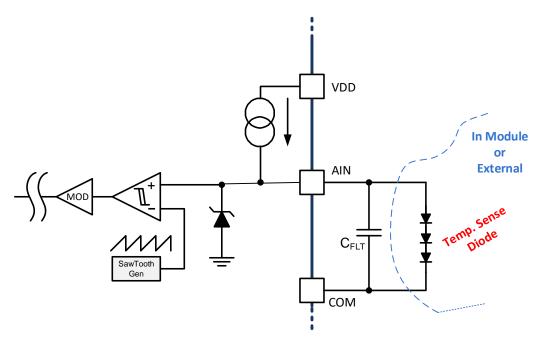

# 8.3.10 Isolated Analog to PWM Signal Function

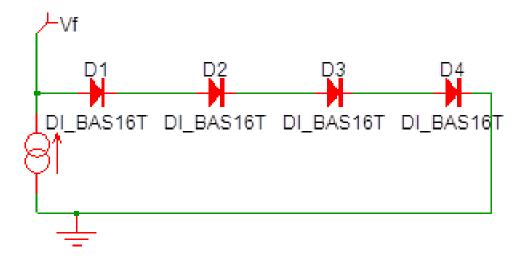

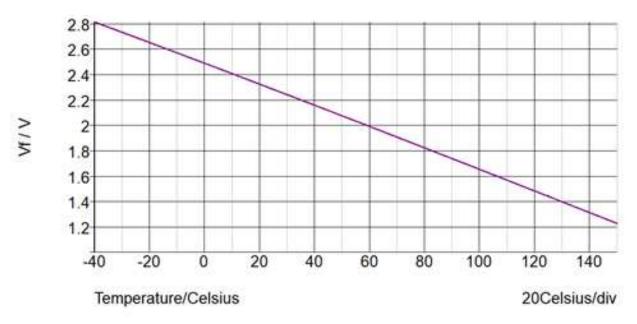

The UCC21710-Q1 features an isolated analog to PWM signal function from AIN to APWM pin, which allows the isolated temperature sensing, high voltage dc bus voltage sensing, etc. An internal current source I<sub>AIN</sub> in AIN pin is implemented in the device to bias an external thermal diode or temperature sensing resistor. The UCC21710-Q1 encodes the voltage signal V<sub>AIN</sub> to a PWM signal, passing through the reinforced isolation barrier, and output to APWM pin on the input side. The PWM signal can either be transferred directly to DSP/MCU to calculate the

4 Submit Documentation Feedback

duty cycle, or filtered by a simple RC filter as an analog signal. The AIN voltage input range is from 0.5V to 4.5V, and the corresponding duty cycle of the APWM output ranges from 90% to 10%. The duty cycle increases linearly from 10% to 90% while the AIN voltage decreases from 4.5V to 0.5V. This corresponds to the temperature coefficient of the negative temperature coefficient (NTC) resistor and thermal diode. When AIN is floating, the AIN voltage is 5V and the APWM operates at 400kHz with approximately 10% duty cycle.

The isolated analog to PWM signal feature can also support other analog signal sensing, such as the high voltage dc bus voltage, etc. The internal current source  $I_{AIN}$  should be taken into account when designing the potential divider if sensing a high voltage.

Figure 17. Isolated Analog to PWM Signal

## 8.4 Device Functional Modes

lists the device function.

**Table 2. Function Table**

|     |      |      | Input | Output |        |     |      |      |               |       |                |

|-----|------|------|-------|--------|--------|-----|------|------|---------------|-------|----------------|

| VCC | VDD  | VEE  | IN+   | IN-    | RST/EN | AIN | RDY  | FLT  | OUTH/<br>OUTL | CLMPI | APWM           |

| PU  | PD   | Х    | Х     | Х      | X      | Х   | Low  | High | Low           | Low   | Low            |

| PD  | PU   | Х    | X     | Х      | Х      | Х   | HiZ  | HiZ  | Low           | Low   | Low            |

| PU  | PU   | Х    | X     | Х      | Low    | Х   | High | High | Low           | Low   | Low            |

| PU  | Open | Х    | X     | Х      | X      | Х   | Low  | HiZ  | HiZ           | HiZ   | HiZ            |

| PU  | PU   | Open | X     | X      | X      | X   | Low  | HiZ  | Low           | Low   | Low            |

| PU  | PU   | Х    | Low   | X      | High   | Х   | High | High | Low           | Low   | $P^*$          |

| PU  | PU   | Х    | Х     | High   | High   | Х   | High | High | Low           | Low   | P <sup>*</sup> |

| PU  | PU   | Х    | High  | Low    | High   | Х   | High | High | High          | HiZ   | P <sup>*</sup> |

PU: Power Up (VCC ≥ 3V, VDD ≥ 12.8V); PD: Power Down (VCC ≤ 2.2V, VDD ≤ 10.4V); X: Irrelevant; P\*: PWM Pulse; HiZ: High Impedance

# 9 Applications and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

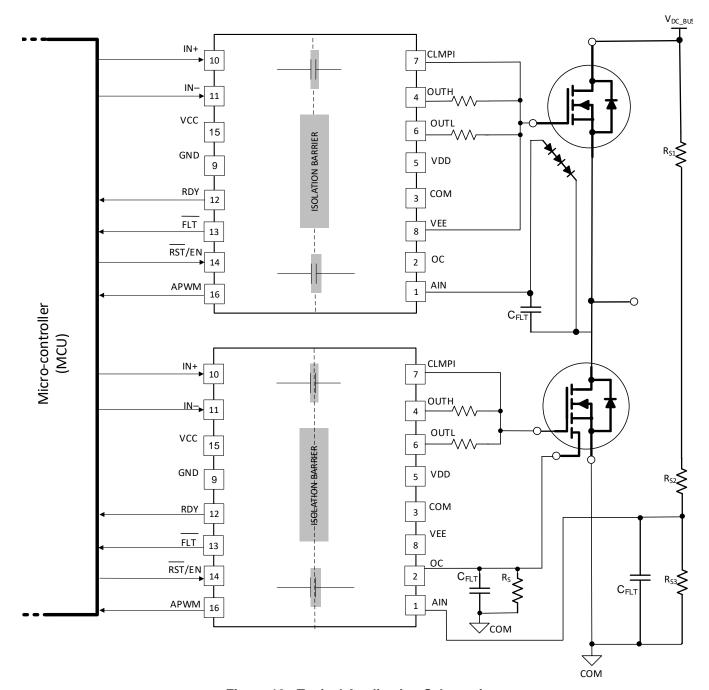

# 9.1 Application Information

The UCC21710-Q1 device is very versatile because of the strong drive strength, wide range of output power supply, high isolation ratings, high CMTI and superior protection and sensing features. The 1.5-kVRMS working voltage and 12.8-kVPK surge immunity can support up to 1700V SiC MOSFET and IGBT. The device is suitable in >10kW power applications such as the traction inverter in HEV/EV, on-board charger and charging pile, motor driver, solar inverter, industrial power supplies and etc. The device can drive the high power SiC MOSFET module, IGBT module or paralleled discrete device directly without traditional buffer drive circuit based on NPN/PNP bipolar transistor in totem-pole structure, which allows the driver to have more control to the power semiconductor and saves the cost and space of the board design. The input side can support 3V, 3.3V, 5V power supply and microcontroller signal, and the device level shifts the signal to output side through isolation barrier. The device has wide output power supply range from 13V to 33V and support wide range of negative power supply. This allows the driver to be used in 20V and -5V SiC MOSFET applications, 15V ad -15V IGBT application and many others. The 12V UVLO benefits the power semiconductor with lower conduction loss and improves the system efficiency. As a reinforced isolated single channel driver, the device can be used to drive either as a low-side or high-side driver.

UCC21710-Q1 device features extensive protection and monitoring features, which can monitor, report and protect the system from various fault conditions.

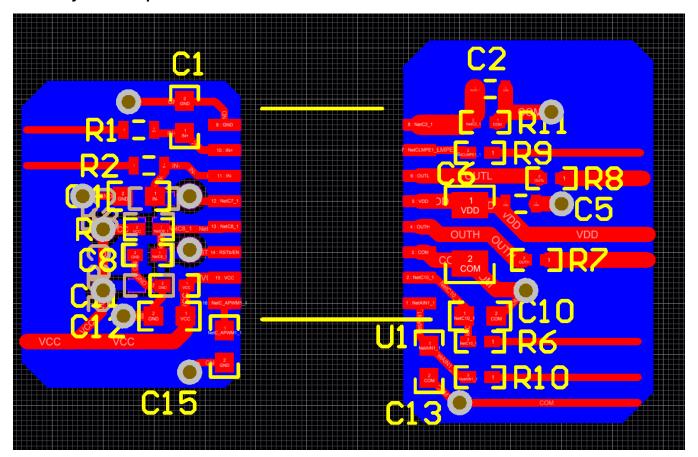

- Fast detection and protection for the overcurrent and short circuit fault. The feature is preferable in a split source SiC MOSFET module or a split emitter IGBT module. For the modules with no integrated current mirror or paralleled discrete semiconductors, the traditional desaturation circuit can be modified to implement short circuit protection. The semiconductor is shutdown when the fault is detected and FLTb pin is pulled down to indicate the fault detection. The device is latched unless reset signal is received from the RST/EN pin.