SLAS594-JULY 2008

# 12-BIT, 3-MSPS, MICROPOWER, MINIATURE SAR ANALOG-TO-DIGITAL CONVERTER

### FEATURES

- 3-MHz Sample Rate Serial Device

- 12-Bit Resolution

- Zero Latency

- 48-MHz Serial Interface

- Supply Range: 2.7 V to 5.5 V

- Low Power Dissipation:

- 6.45 mW at 3-V V<sub>DD</sub>, 2 MSPS

- 13.5 mw at 5-V V<sub>DD</sub>, 3 MSPS

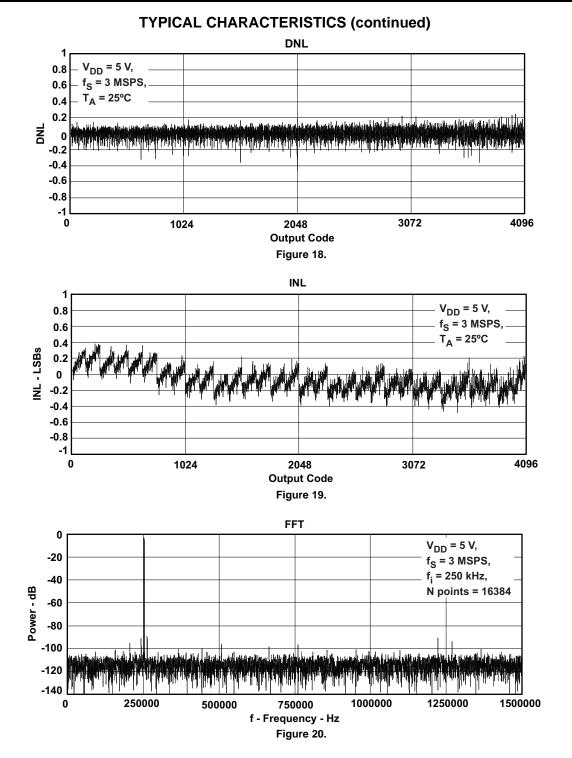

- ±0.6 LSB INL, ±0.5 LSB DNL

- 72 dB SINAD, -84 dB THD

- Unipolar Input Range: 0 V to V<sub>DD</sub>

- Power-Down Current: 1 µA

- Wide Input Bandwidth: 30 MHz at 3 dB

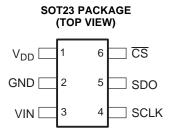

- 6-Pin SOT23 Package

## DESCRIPTION

## APPLICATIONS

- Base Band Converters in Radio

Communication

- Motor Current/Bus Voltage Sensors in Digital Drives

- Optical Networking (DWDM, MEMS Based Switching)

- Optical Sensors

- Battery Powered Systems

- Medical Instrumentations

- High-Speed Data Acquisition Systems

- High-Speed Closed-Loop Systems

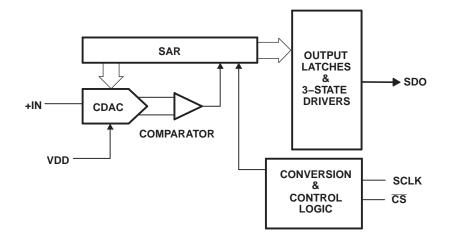

The ADS7883 is a 12-bit, 3-MSPS analog-to-digital converter (ADC). The device includes a capacitor based SAR A/D converter with inherent sample and hold. The serial interface in the device is controlled by the CS and SCLK signals for glueless connections with microprocessors and DSPs. The input signal is sampled with the falling edge of CS, and SCLK is used for conversion and serial data output.

The device operates from a wide supply range from 2.7 V to 5.5 V. The low power consumption of the device makes it suitable for battery-powered applications. The device also includes a power saving power-down feature for when the device is operated at lower conversion speeds.

The high level of the digital input to the device is not limited to device  $V_{DD}$ . Therefore the digital input can go as high as 5.5 V when the device supply is 2.7 V. This feature is useful when digital signals are received from another circuit with different supply levels. This also reduces restrictions on power-up sequencing.

The ADS7883 is available in a 6-pin SOT23 package and is specified for operation from -40°C to 125°C.

| BIT    | < 300 KSPS                                            | 300 KSPS – 1.25 MSPS                                    |                                                       | 3 MSPS                                                |

|--------|-------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

| 12-Bit |                                                       | ADS7886 (2.35 V <sub>DD</sub> to 5.25 V <sub>DD</sub> ) | ADS7883                                               | 3 MSPS for 4.5 $V_{\text{DD}}$ to 5.5 $V_{\text{DD}}$ |

| 12-DIL | ADS7866 (1.2 V <sub>DD</sub> to 3.6 V <sub>DD</sub> ) | AD37666 (2.35 V <sub>DD</sub> 10 5.25 V <sub>DD</sub> ) | AD31003                                               | 2 MSPS for 2.7 $V_{\text{DD}}$ to 4.5 $V_{\text{DD}}$ |

| 10-Bit | ADS7867 (1.2 $V_{\text{DD}}$ to 3.6 $V_{\text{DD}}$ ) | ADS7887 (2.35 $V_{\text{DD}}$ to 5.25 $V_{\text{DD}}$ ) | ADS7884 (2.7 V <sub>DD</sub> to 5.5 V <sub>DD</sub> ) |                                                       |

| 8-Bit  | ADS7868 (1.2 $V_{DD}$ to 3.6 $V_{DD}$ )               | ADS7888 (2.35 $V_{\text{DD}}$ to 5.25 $V_{\text{DD}}$ ) | ADS7885 (2                                            | 2.7 V <sub>DD</sub> to 5.5 V <sub>DD</sub> )          |

#### **MicroPower Miniature SAR Converter Family**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## ADS7883

#### SLAS594-JULY 2008

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### PACKAGE/ORDERING INFORMATION<sup>(1)</sup>

| DEVICE    | MAXIMUM<br>INTEGRAL<br>LINEARITY<br>(LSB) | MAXIMUM<br>DIFFERENTIAL<br>LINEARITY<br>(LSB) | NO MISSING<br>CODES AT<br>RESOLUTION<br>(BIT) | PACKAGE<br>TYPE | PACKAGE<br>DESIGNAT<br>OR | TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>INFORMATION | TRANSPORT<br>MEDIA<br>QUANTITY |

|-----------|-------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------|---------------------------|----------------------|--------------------|-------------------------|--------------------------------|

| ADS7883SB | ±1                                        | ±1                                            | 12                                            | 6-Pin<br>SOT23  | DBV                       |                      | 7883               | ADS7883SBDBVT           | Small Tape and<br>Reel 250     |

| AD370033D | ΞI                                        | ΞI                                            | 12                                            |                 |                           | –40°C to 125°C       | 7883               | ADS7883SBDBVR           | Large Tape and<br>Reel 3000    |

| 40679936  | ±2                                        | ±2                                            | 11                                            |                 |                           |                      | 7883               | ADS7883SDBVT            | Small Tape and<br>Reel 250     |

| ADS7883S  | ±Ζ                                        |                                               |                                               |                 |                           |                      | 7883               | ADS7883SDBVR            | Large Tape and<br>Reel 3000    |

(1) For most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

|                                           |                                      | UNIT                                                 |

|-------------------------------------------|--------------------------------------|------------------------------------------------------|

| +IN to AGND                               |                                      | –0.3 V to +V <sub>DD</sub> +0.3 V                    |

| +V <sub>DD</sub> to AGND                  |                                      | –0.3 V to 7.0 V                                      |

| Digital input voltage to GND              |                                      | -0.3 V to (7.0 V)                                    |

| Digital output to GND                     | -0.3 V to (+V <sub>DD</sub> + 0.3 V) |                                                      |

| Operating temperature range               | -40°C to 125°C                       |                                                      |

| Storage temperature range                 | –65°C to 150°C                       |                                                      |

| Junction temperature (T <sub>J</sub> Max) |                                      | 150°C                                                |

| Power dissipation, SOT23 packa            | ge                                   | (Τ <sub>J</sub> Max–T <sub>A</sub> )/θ <sub>JA</sub> |

| Thermal impedance, $\theta_{JA}$          | SOT23                                | 295.2°C/W                                            |

| Lead temperature, soldering               | Vapor phase (60 sec)                 | 215°C                                                |

| Leau temperature, soldering               | Infrared (15 sec)                    | 220°C                                                |

(1) Stresses above those listed under *absolute maximum ratings* may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

#### www.ti.com

### **ELECTRICAL SPECIFICATIONS**

v

|                   | PARAMETER                                   |                    | TEST CONDITIONS                                                          | MIN                  | TYP   | MAX                  | UNIT              |

|-------------------|---------------------------------------------|--------------------|--------------------------------------------------------------------------|----------------------|-------|----------------------|-------------------|

| ANALO             | g input                                     |                    |                                                                          |                      |       |                      |                   |

|                   | Full-scale input voltage s                  | pan <sup>(1)</sup> |                                                                          | 0                    |       | V <sub>DD</sub>      | V                 |

|                   | Absolute input voltage ra                   | nge                | +IN                                                                      | -0.2                 |       | V <sub>DD</sub> +0.2 | V                 |

| CI                | Input capacitance <sup>(2)</sup>            |                    |                                                                          |                      | 27    |                      | pF                |

| l <sub>likg</sub> | Input leakage current                       |                    | T <sub>A</sub> = 125°C                                                   |                      | 40    |                      | nA                |

| v                 | M PERFORMANCE                               |                    |                                                                          |                      |       |                      | L                 |

|                   | Resolution                                  |                    |                                                                          |                      | 12    |                      | Bits              |

|                   |                                             | ADS7883SB          |                                                                          | 12                   |       |                      |                   |

|                   | No missing codes                            | ADS7883S           |                                                                          | 11                   |       |                      | Bits              |

|                   |                                             | ADS7883SB          |                                                                          | -1                   | ±0.6  | 1                    | (0                |

| INL               | Integral nonlinearity                       | ADS7883S           |                                                                          | -2                   | ±0.75 | 2                    | LSB <sup>(3</sup> |

|                   |                                             | ADS7883SB          |                                                                          | -1                   | ±0.5  | 1                    |                   |

| DNL               | Differential nonlinearity ADS7883S          |                    |                                                                          | -2                   | ±0.75 | 2                    | LSB               |

| Eo                | Offset error <sup>(4)(5)(6)</sup>           | 1.2010000          |                                                                          | -3                   | ±0.2  | 3                    |                   |

| E <sub>G</sub>    | Gain error <sup>(5)</sup>                   |                    |                                                                          | -3.5                 | ±0.2  | 3.5                  | LSB               |

|                   |                                             |                    |                                                                          | 0.0                  | 10.0  | 0.0                  | LOD               |

|                   |                                             |                    | 32-MHz SCLK, V <sub>DD</sub> = 3 V                                       | 398                  | 422   |                      |                   |

|                   | Conversion time                             |                    |                                                                          | 265                  | 281   |                      | ns                |

|                   |                                             |                    | 48-MHz SCLK, V <sub>DD</sub> = 5 V<br>32-MHz SCLK, V <sub>DD</sub> = 3 V |                      | 201   |                      |                   |

|                   | Acquisition time<br>Maximum throughput rate |                    |                                                                          | 78                   |       |                      | ns                |

|                   |                                             |                    | $48-MHz SCLK, V_{DD} = 5 V$                                              | 52                   |       |                      |                   |

|                   |                                             |                    | 32-MHz SCLK, V <sub>DD</sub> = 2.7 V to 4.5 V                            |                      |       | 2                    | MHz               |

|                   |                                             |                    | 48-MHz SCLK, $V_{DD}$ = 4.5 V to 5.5 V                                   |                      |       | 3                    |                   |

|                   | Aperture delay                              |                    |                                                                          |                      | 10    |                      | ns                |

|                   | IC CHARACTERISTICS                          | (                  |                                                                          | i                    |       |                      | 1                 |

| THD               | Total harmonic distortion                   | (7)                | $f_I = 100 \text{ kHz}$                                                  |                      | -84   |                      | dB                |

| SINAD             | Signal-to-noise and disto                   | rtion              | f <sub>l</sub> = 100 kHz, ADS7883SB                                      | 69                   | 72    |                      | dB                |

| 0                 | eignai te nelee ana alete                   |                    | f <sub>l</sub> = 100 kHz, ADS7883S                                       | 68                   | 70    |                      |                   |

| SFDR              | Spurious free dynamic ra                    | nge                | f <sub>I</sub> = 100 kHz                                                 |                      | 86    |                      | dB                |

|                   | Full power bandwidth                        |                    | At –3 dB                                                                 | 30                   |       |                      | MHz               |

| DIGITAL           | L INPUT/OUTPUT                              |                    |                                                                          |                      |       |                      |                   |

| Logic fai         | mily — CMOS                                 |                    |                                                                          |                      |       |                      |                   |

| M                 |                                             |                    | V <sub>DD</sub> = 2.7 V to 3.6 V                                         | 1.5                  |       | 5.5                  | N                 |

| V <sub>IH</sub>   | High-level input voltage                    |                    | V <sub>DD</sub> = 3.6 V to 5.5 V                                         | 2.2                  |       | 5.5                  | V                 |

|                   | Law law line in the                         |                    | V <sub>DD</sub> = 2.7 V to 3.6 V                                         |                      |       | 0.4                  |                   |

| V <sub>IL</sub>   | Low-level input voltage                     |                    | V <sub>DD</sub> = 3.6 V to 5.5 V                                         |                      |       | 0.8                  | V                 |

| V <sub>OH</sub>   | High-level output voltage                   |                    | At I <sub>source</sub> = 200 μA                                          | V <sub>DD</sub> -0.2 |       |                      |                   |

| V <sub>OL</sub>   | Low-level output voltage                    |                    | At $I_{sink} = 200 \ \mu A$                                              |                      |       | 0.4                  | 4 V               |

|                   |                                             | S                  |                                                                          | 1                    |       |                      | <u>I</u>          |

| +V <sub>DD</sub>  | Supply voltage                              |                    |                                                                          | 2.7                  | 3.3   | 5.5                  | V                 |

(1) Ideal input span; does not include gain or offset error

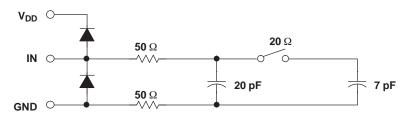

Refer to Figure 24 for details on sampling circuit (2)

(3) LSB means least significant bit

- Measured relative to an ideal full-scale input (4)

- (5)

(6)

Offset error and gain error ensured by characterization First transition of 000H to 001H at  $(V_{ref}/2^{10})$ Calculated on the first nine harmonics of the input frequency (7)

Copyright © 2008, Texas Instruments Incorporated

#### SLAS594-JULY 2008

### **ELECTRICAL SPECIFICATIONS (continued)**

$V_{\text{DD}}$  = 2.7 V to 5.5 V,  $T_{\text{A}}$  = –40°C to 125°C,  $f_{\text{sample}}$  = 2 MSPS for  $V_{\text{DD}}$  = 2.7 V to 4.5 V,  $f_{\text{sample}}$  = 3 MSPS for  $V_{\text{DD}}$  = 4.5 V to 5.5 V

| PARAMETER                          | TEST CONDITIONS                      | MIN TYP | MAX  | UNIT |

|------------------------------------|--------------------------------------|---------|------|------|

|                                    | At $V_{DD}$ = 3 V, 2-MSPS throughput | 2.15    | 3    |      |

| Supply surrent (normal mode)       | At $V_{DD}$ = 3 V, Static state      | 1.8     |      | A    |

| Supply current (normal mode)       | At $V_{DD}$ = 5 V, 3-MSPS throughput | 2.7     | 4    | mA   |

|                                    | At $V_{DD}$ = 5 V, Static state      | 2       |      |      |

|                                    | SCLK off                             |         | 1    |      |

| Power-down state supply current    | SCLK on (48 MHz)                     | 90      | 250  | μA   |

| Davier diasis ation                | V <sub>DD</sub> = 5 V, 3 MSPS        | 13.5    | 20   |      |

| Power dissipation                  | V <sub>DD</sub> = 3 V, 2 MSPS        | 6.45    |      | mW   |

| Device disaination in static state | $V_{DD} = 5 V$                       | 10      | 12.5 |      |

| Power dissipation in static state  | V <sub>DD</sub> = 3 V                | 5.4     |      | mW   |

| Power-down time                    |                                      |         | 0.1  | μs   |

| Power-up time                      |                                      |         | 0.8  | μs   |

| EMPERATURE RANGE                   |                                      |         |      |      |

| Specified performance              |                                      | -40     | 125  | °C   |

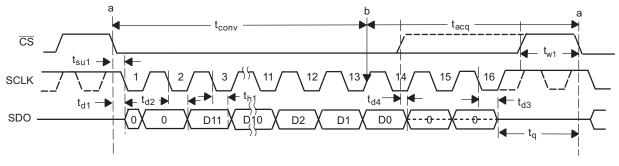

## TIMING REQUIREMENTS (see Figure 21)

All specifications typical at  $T_A = -40^{\circ}C$  to 125°C,  $V_{DD} = 2.7$  V to 5.5 V, unless otherwise specified.

|                   | PARAMETER                                             | TEST CONDITIONS <sup>(1)</sup> | MIN                      | TYP | MAX                      | UNIT |  |  |  |  |

|-------------------|-------------------------------------------------------|--------------------------------|--------------------------|-----|--------------------------|------|--|--|--|--|

|                   | Conversion time                                       | $V_{DD} = 3 V$                 |                          |     | 13.5 × t <sub>SCLK</sub> |      |  |  |  |  |

| t <sub>conv</sub> | Conversion time                                       | V <sub>DD</sub> = 5 V          |                          |     | 13.5 × t <sub>SCLK</sub> | ns   |  |  |  |  |

|                   | A guidition time                                      | $V_{DD} = 3 V$                 | 78                       |     |                          |      |  |  |  |  |

| t <sub>acq</sub>  | Aquisition time                                       | $V_{DD} = 5 V$                 | 52                       |     |                          | ns   |  |  |  |  |

|                   | Minimum quiet time needed from bus 3-state to start   | $V_{DD} = 3 V$                 | 10                       |     |                          | -    |  |  |  |  |

| tq                | of next conversion                                    | $V_{DD} = 5 V$                 | 10                       |     |                          | ns   |  |  |  |  |

|                   | Delay time, $\overline{CS}$ low to first data (0) out | $V_{DD} = 3 V$                 |                          | 9   | 15                       | 20   |  |  |  |  |

| t <sub>d1</sub>   | Delay lime, CS low to hist data (0) out               | $V_{DD} = 5 V$                 |                          | 8   | 11                       | ns   |  |  |  |  |

|                   | Setup time, $\overline{CS}$ low to SCLK low           | $V_{DD} = 3 V$                 | 7                        |     |                          |      |  |  |  |  |

| t <sub>su1</sub>  | Setup time, CS low to SCLK low                        | $V_{DD} = 5 V$                 | 5                        |     |                          | ns   |  |  |  |  |

|                   | Delay time, SCLK falling to SDO                       | $V_{DD} = 3 V$                 |                          | 11  | 20                       | ns   |  |  |  |  |

| t <sub>d2</sub>   | Delay lime, SCLK failing to SDO                       | $V_{DD} = 5 V$                 |                          | 9   | 12                       | 115  |  |  |  |  |

| •                 | Hold time, SCLK falling to data valid <sup>(2)</sup>  | V <sub>DD</sub> < 3 V          | 5.5                      |     |                          | 20   |  |  |  |  |

| t <sub>h1</sub>   |                                                       | $V_{DD} > 5 V$                 | 4                        |     |                          | ns   |  |  |  |  |

|                   | Delay time, 16th SCI K falling adap to SDO 2 state    | $V_{DD} = 3 V$                 |                          | 9   | 15                       |      |  |  |  |  |

| t <sub>d3</sub>   | Delay time, 16th SCLK falling edge to SDO 3-state     | $V_{DD} = 5 V$                 |                          | 8   | 11                       | ns   |  |  |  |  |

|                   | Pulse duration, $\overline{CS}$                       | $V_{DD} = 3 V$                 | 10                       |     |                          |      |  |  |  |  |

| t <sub>w1</sub>   | Pulse duration, CS                                    | $V_{DD} = 5 V$                 | 10                       |     |                          | ns   |  |  |  |  |

|                   | Delay time, $\overline{CS}$ high to SDO 3-state,      | $V_{DD} = 3 V$                 |                          | 9   | 15                       |      |  |  |  |  |

| t <sub>d4</sub>   | Delay time, CS high to SDO 3-state,                   | $V_{DD} = 5 V$                 |                          | 8   | 11                       | ns   |  |  |  |  |

|                   | Dulas duration SCLK high                              | $V_{DD} = 3 V$                 | 0.45 × t <sub>SCLK</sub> |     |                          | 20   |  |  |  |  |

| t <sub>wH</sub>   | Pulse duration, SCLK high                             | $V_{DD} = 5 V$                 | 0.45 × t <sub>SCLK</sub> |     |                          | ns   |  |  |  |  |

|                   | Pulse duration SCLK low                               | $V_{DD} = 3 V$                 | 0.45 × t <sub>SCLK</sub> |     |                          |      |  |  |  |  |

| t <sub>wL</sub>   | Pulse duration, SCLK low                              | V <sub>DD</sub> = 5 V          | 0.45 × t <sub>SCLK</sub> |     |                          |      |  |  |  |  |

(1) 3-V Specifications apply from 2.7 V to 3.6 V, and 5-V specifications apply from 4.5 V to 5.5 V.

4 Submit Documentation Feedback

<sup>(2)</sup> With 10-pf load.

## TIMING REQUIREMENTS (see Figure 21) (continued)

All specifications typical at  $T_A = -40^{\circ}C$  to 125°C,  $V_{DD} = 2.7$  V to 5.5 V, unless otherwise specified.

|                 | PARAMETER                                                                            | TEST CONDITIONS <sup>(1)</sup>   | MIN | TYP | MAX | UNIT  |

|-----------------|--------------------------------------------------------------------------------------|----------------------------------|-----|-----|-----|-------|

|                 |                                                                                      | V <sub>DD</sub> = 2.7 V to 4.5 V |     |     | 32  | N411- |

|                 | Frequency, SCLK                                                                      | V <sub>DD</sub> = 4.5 V to 5.5 V |     |     | 48  | MHz   |

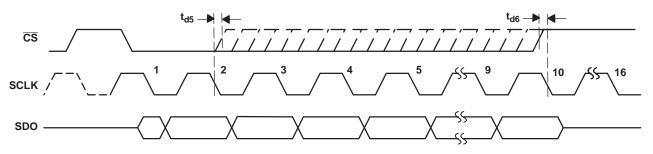

|                 | Delay time, second falling edge of clock and $\overline{CS}$ to                      | V <sub>DD</sub> = 3 V            | -2  |     | 4   |       |

| t <sub>d5</sub> | enter in powerdown (use min spec not to accidently enter in powerdown) see Figure 22 | V <sub>DD</sub> = 5 V            | -2  |     | 3   | ns    |

|                 | Delay time, $\overline{CS}$ and 10th falling edge of clock to enter                  | V <sub>DD</sub> = 3 V            | -2  |     | 4   |       |

| t <sub>d6</sub> | in powerdown (use max spec not to accidently enter<br>in powerdown) see Figure 22    | V <sub>DD</sub> = 5 V            | -2  |     | 3   | ns    |

### **DEVICE INFORMATION**

### **TERMINAL FUNCTIONS**

| TER             | TERMINAL |       | DESCRIPTION                                                                                    |  |  |  |  |  |

|-----------------|----------|-------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME            | NO.      | - I/O | DESCRIPTION                                                                                    |  |  |  |  |  |

| V <sub>DD</sub> | 1        | -     | Power supply input, also acts like a reference voltage to ADC.                                 |  |  |  |  |  |

| GND             | 2        | -     | Ground for power supply, all analog and digital signals are referred with respect to this pin. |  |  |  |  |  |

| VIN             | 3        | I     | Analog signal input                                                                            |  |  |  |  |  |

| SCLK            | 4        | I     | Serial clock                                                                                   |  |  |  |  |  |

| SDO             | 5        | 0     | Serial data out                                                                                |  |  |  |  |  |

| CS              | 6        | I     | Chip select signal, active low                                                                 |  |  |  |  |  |

www.ti.com

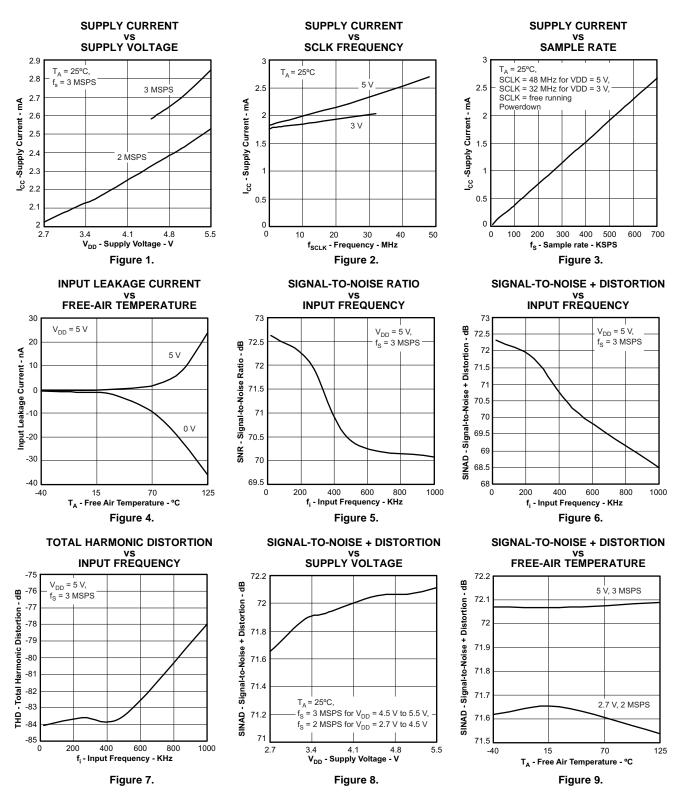

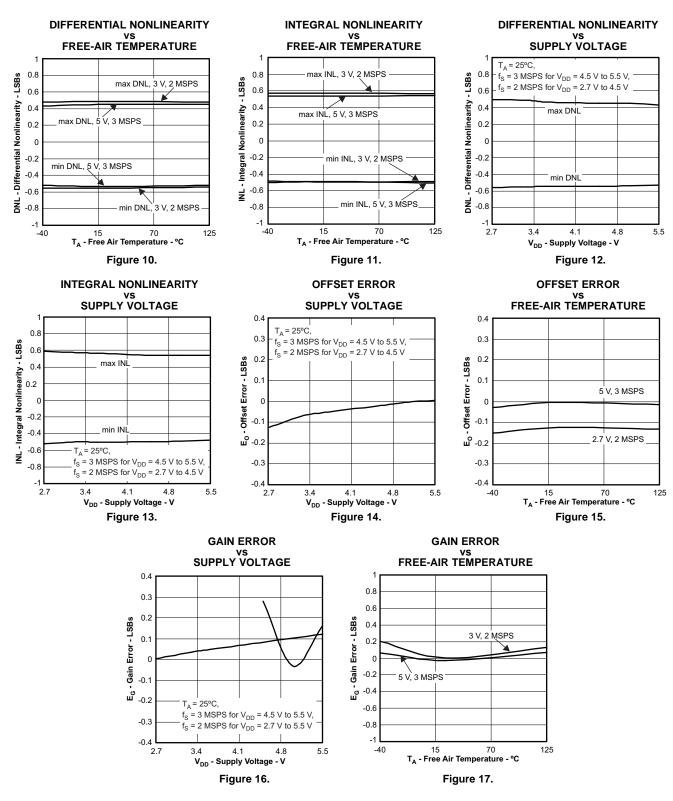

### **TYPICAL CHARACTERISTICS**

www.ti.com

### **TYPICAL CHARACTERISTICS (continued)**

## ADS7883

SLAS594-JULY 2008

Texas Instruments

www.ti.com

#### NORMAL OPERATION

The cycle begins with the falling edge of  $\overline{CS}$ . This point is indicated as **a** in Figure 21. With the falling edge of  $\overline{CS}$ , the input signal is sampled and the conversion process is initiated. The device outputs data while the conversion is in progress. The data word contains two leading zeros, followed by 12-bit data in MSB first format and padded by two lagging zeros.

The falling edge of  $\overline{CS}$  clocks out the first zero, and a second zero is clocked out on the first falling edge of the clock. Data is in MSB first format with the MSB being clocked out on the 2nd falling edge. Data is padded with two lagging zeros as shown in Figure 21. The conversion ends on the first rising edge of SCLK after the 13th falling edge. At this point the device enters the acquisition phase. This point is indicated by **b** in Figure 21.

Figure 21 shows the device data is read in a sixteen clock frame. However,  $\overline{CS}$  can be asserted (pulled high) any time after point **b**. SDO goes to 3-state with the  $\overline{CS}$  high level. The next conversion should not be started (by pulling  $\overline{CS}$  low) until the end of the quiet sampling time (t<sub>q</sub>) after SDO goes to 3-state or until the minimum acquisition time (t<sub>acq</sub>) has elapsed. To continue normal operation, it is necessary that  $\overline{CS}$  is not pulled high until point **b**. Without this, the device does not enter the acquisition phase and no valid data is available in the next cycle. (Also refer to the Power-Down Mode section for more details.)  $\overline{CS}$  going high any time during the conversion aborts the ongoing conversion and SDO goes to 3-state.

The high level of the digital input to the device is not limited to device  $V_{DD}$ . This means the digital input can go as high as 5.5 V when the device supply is 2.7 V. This feature is useful when digital signals are received from another circuit with different supply levels. Also, this relaxes the restriction on power-up sequencing. However, the digital output levels ( $V_{OH}$  and  $V_{OL}$ ) are governed by  $V_{DD}$  as listed in the Electrical Specifications table.

Figure 21. Interface Timing Diagram

#### **POWER-DOWN MODE**

The device enters power-down mode if  $\overline{CS}$  goes high anytime after the 2nd SCLK falling edge to before the 10th SCLK falling edge. An ongoing conversion stops and SDO goes to 3-state under this power-down condition as shown in Figure 22.

Figure 22. Entering Power-Down Mode

SLAS594-JULY 2008

#### SLAS594-JULY 2008

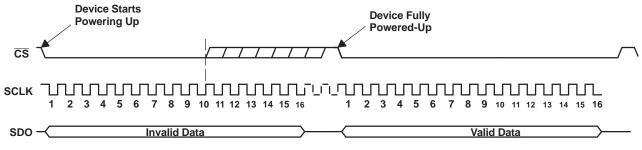

A dummy cycle with  $\overline{CS}$  low for more than 10 SCLK falling edges brings the device out of power-down mode. For the device to reach the fully powered up condition requires 0.8 µs.  $\overline{CS}$  can be pulled high any time after the 10th falling edge as shown in Figure 23. Note that the power-up time of 0.8 µs is more than a single conversion cycle at 3-MSPS speed. This means the device requires three dummy conversion frames at 3-MSPS speed or one elongated dummy conversion frame. The data during the dummy conversion frames is invalid.

Figure 23. Exiting Power-Down Mode

#### APPLICATION INFORMATION

Figure 24. Typical Equivalent Sampling Circuit

#### Driving the VIN and $V_{DD}$ Pins

The VIN input to the ADS7883 should be driven with a low impedance source. In most cases additional buffers are not required. In cases where the source impedance exceeds 200  $\Omega$ , using a buffer would help achieve the rated performance of the converter. The THS4031 is a good choice for the driver amplifier buffer.

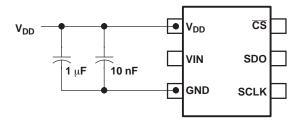

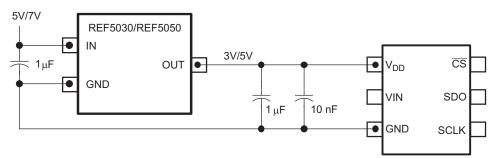

The reference voltage for the ADS7883 A/D converter is derived from the supply voltage internally. The device offers limited low-pass filtering functionality on-chip. The supply to these converters should be driven with a low impedance source and should be decoupled to the ground. A  $1-\mu F$  storage capacitor and a 10-nF decoupling capacitor should be placed close to the device. Wide, low impedance traces should be used to connect the capacitor to the pins of the device. The ADS7883 draws very little current from the supply lines. The supply line can be driven by either:

- Directly from the system supply.

- A reference output from a low drift and low drop out reference voltage generator like the REF5030 or REF5050. The ADS7883 can operate with a wide range of supply voltages. The actual choice of the reference voltage generator depends upon the system. Figure 26 shows one possible application circuit.

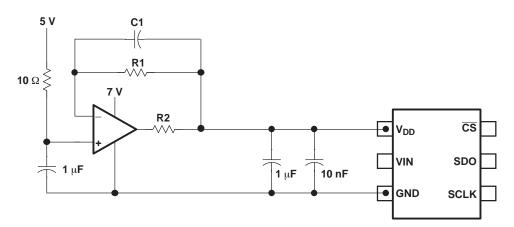

- A low-pass filtered version of the system supply followed by a buffer like the zero-drift OPA735 can also be used in cases where the system power supply is noisy. Care should be taken to ensure that the voltage at the V<sub>DD</sub> input does not exceed 7 V (especially during power up) to avoid damage to the converter. This can be done easily using single supply CMOS amplifiers like the OPA735. Figure 27 shows one possible application circuit.

Figure 25. Supply/Reference Decoupling Capacitors

www.ti.com

Figure 27. Buffering with the OPA735

### **PACKAGING INFORMATION**

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)            | Lead/Ball Finish<br>(6) | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|----------------------------|-------------------------|---------------------|--------------|-------------------------|---------|

| ADS7883SBDBVR    | ACTIVE        | SOT-23       | DBV                | 6    | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU               | Level-2-260C-1 YEAR | -40 to 125   | 7883                    | Samples |

| ADS7883SBDBVT    | ACTIVE        | SOT-23       | DBV                | 6    | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU               | Level-2-260C-1 YEAR | -40 to 125   | 7883                    | Samples |

| ADS7883SDBVR     | ACTIVE        | SOT-23       | DBV                | 6    | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU               | Level-2-260C-1 YEAR | -40 to 125   | 7883                    | Samples |

| ADS7883SDBVT     | ACTIVE        | SOT-23       | DBV                | 6    | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU               | Level-2-260C-1 YEAR | -40 to 125   | 7883                    | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

8-May-2018

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## **PACKAGE MATERIALS INFORMATION**

www.ti.com

Texas Instruments

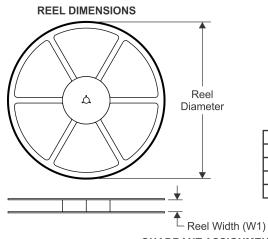

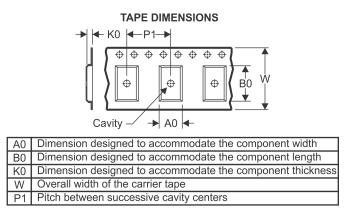

### **TAPE AND REEL INFORMATION**

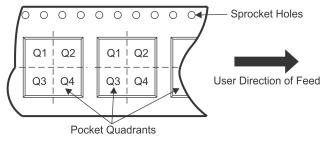

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal<br>Device | 1      | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------------------------------|--------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ADS7883SBDBVR                         | SOT-23 | DBV                | 6 | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| ADS7883SBDBVT                         | SOT-23 | DBV                | 6 | 250  | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| ADS7883SDBVR                          | SOT-23 | DBV                | 6 | 3000 | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| ADS7883SDBVT                          | SOT-23 | DBV                | 6 | 250  | 180.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

TEXAS INSTRUMENTS

www.ti.com

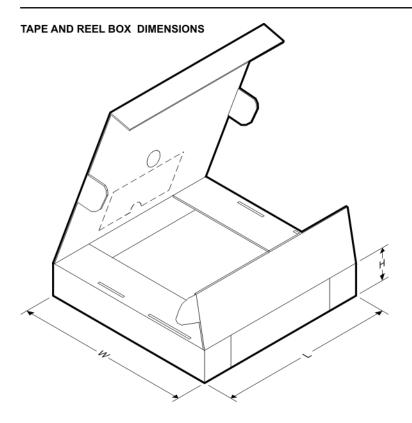

## PACKAGE MATERIALS INFORMATION

11-May-2018

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ADS7883SBDBVR | SOT-23       | DBV             | 6    | 3000 | 195.0       | 200.0      | 45.0        |

| ADS7883SBDBVT | SOT-23       | DBV             | 6    | 250  | 195.0       | 200.0      | 45.0        |

| ADS7883SDBVR  | SOT-23       | DBV             | 6    | 3000 | 195.0       | 200.0      | 45.0        |

| ADS7883SDBVT  | SOT-23       | DBV             | 6    | 250  | 195.0       | 200.0      | 45.0        |

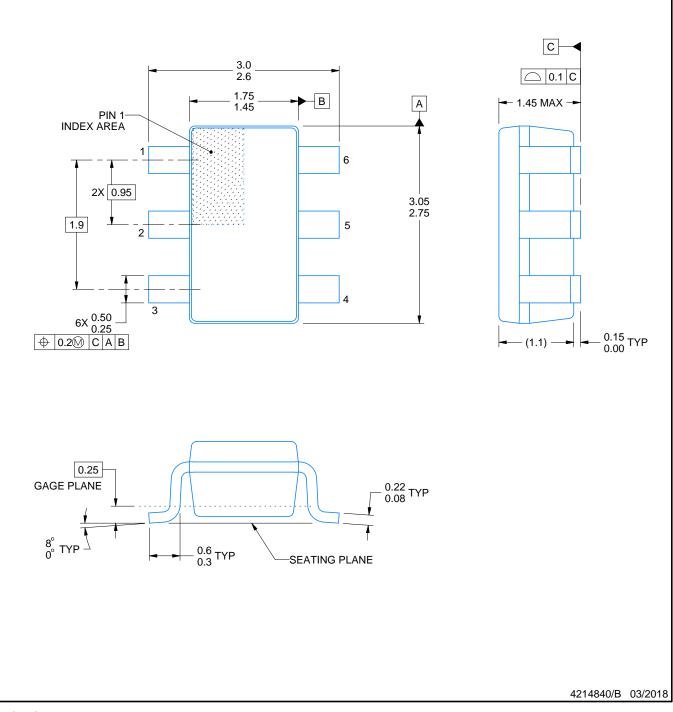

# **DBV0006A**

## **PACKAGE OUTLINE**

SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.2. This drawing is subject to change without notice.3. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- 4. Leads 1,2,3 may be wider than leads 4,5,6 for package orientation. 5. Refernce JEDEC MO-178.

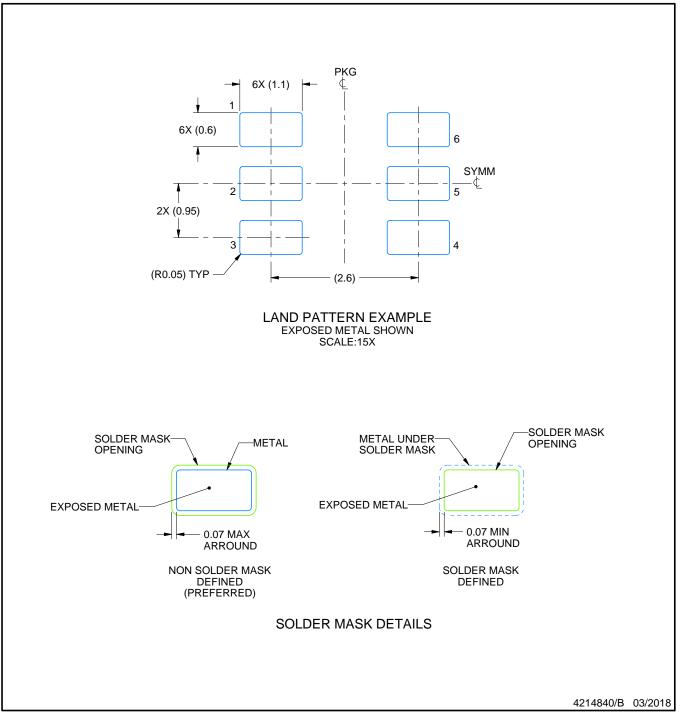

# **DBV0006A**

# **EXAMPLE BOARD LAYOUT**

## SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

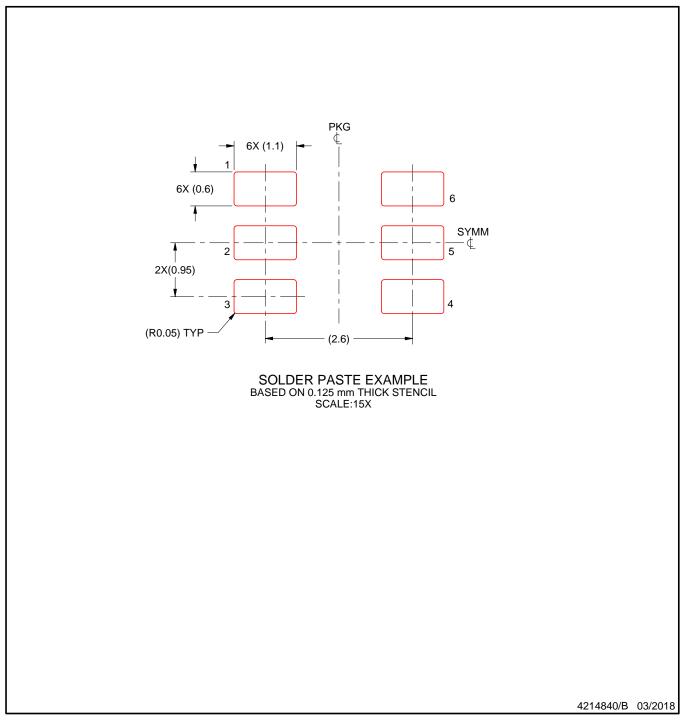

## **DBV0006A**

# **EXAMPLE STENCIL DESIGN**

## SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated