# 5.7 kV rms, Signal Isolated, Basic CAN FD Transceiver

Data Sheet ADM3050E

#### **FEATURES**

5.7 kV rms signal isolated CAN FD transceiver

1.7 V to 5.5 V supply and logic side levels

4.5 V to 5.5 V supply on bus side

ISO 11898-2:2016-compliant CAN FD

Data rates up to 12 Mbps for CAN FD

Low maximum loop propagation delay: 150 ns

Extended common-mode range: ±25 V

Bus fault protection (CANH, CANL): ±40 V Passes EN 55022, Class B by 6 dB Safety and regulatory approvals

VDE certificate of conformity, VDE V 0884-10 (pending)

UL: 5700 V rms for 1-minute duration per UL 1577 (pending)

CSA component acceptance 5A at 5.7 kV rms

IEC 60950, IEC 61010 (pending)

High common-mode transient immunity: >75 kV/ $\mu$ s Industrial operating temperature range:  $-40^{\circ}$ C to  $+125^{\circ}$ C

#### **APPLICATIONS**

CANOpen, DeviceNet, and other CAN bus implementations Industrial automation

Process control and building control

Transport and infrastructure

### **GENERAL DESCRIPTION**

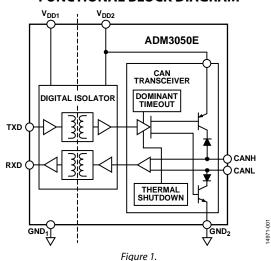

The ADM3050E is a 5.7 kV rms isolated controller area network (CAN) physical layer transceiver with a high performance, basic feature set. The ADM3050E fully meets the CAN flexible data rate (CAN FD) ISO 11898-2:2016 requirements and is further capable of supporting data rates as high as 12 Mbps.

The device employs Analog Devices, Inc., *i*Coupler® technology to combine a 2-channel isolator and a CAN transceiver into a single small outline integrated circuit (SOIC) surface-mount package. The ADM3050E is a fully isolated solution for CAN and CAN FD applications. The ADM3050E provides isolation between the CAN controller and physical layer bus. Safety and regulatory approvals (pending) for a 5.7 kV rms withstand voltage, an 849 V<sub>PEAK</sub> working voltage, and a 12.8 kV surge test, ensure that the ADM3050E meets application isolation requirements.

#### **FUNCTIONAL BLOCK DIAGRAM**

Low loop propagation delays and the extended common-mode range of  $\pm 25$  V support robust communication on longer bus cables. Dominant timeout functionality protects against bus lock up in a fault condition, and current limiting and thermal shutdown features protect against output short circuits. The CAN bus input and output pins are protected to  $\pm 40$  V against accidental connection to a  $\pm 24$  V bus supply. The device is fully specified over the  $\pm 40$ °C to  $\pm 125$ °C industrial temperature range.

# **TABLE OF CONTENTS**

| Features                                                                                                           | . 1 |

|--------------------------------------------------------------------------------------------------------------------|-----|

| Applications                                                                                                       | . 1 |

| Functional Block Diagram                                                                                           | . 1 |

| General Description                                                                                                | . 1 |

| Revision History                                                                                                   | . 2 |

| Specifications                                                                                                     | . 3 |

| Timing Specifications                                                                                              | . 5 |

| Timing Diagrams                                                                                                    | . 5 |

| Insulation and Safety Related Specifications                                                                       | 6   |

| Package Characteristics                                                                                            | 6   |

| Regulatory Information                                                                                             | . 6 |

| DIN V VDE V 0884-10 (VDE V 0884-10) Insulation<br>Characteristics (Pending)                                        | . 7 |

| Absolute Maximum Ratings                                                                                           | . 8 |

| Thermal Resistance                                                                                                 | . 8 |

| ESD Caution                                                                                                        | . 8 |

| Pin Configuration and Function Descriptions                                                                        | 9   |

| Operational Truth Table                                                                                            | 9   |

| Typical Performance Characteristics                                                                                | 10  |

| Test Circuits                                                                                                      | 12  |

| Terminology                                                                                                        | 13  |

| REVISION HISTORY                                                                                                   |     |

| 12/2018—Rev. 0 to Rev. A                                                                                           |     |

| Change to Features Section                                                                                         |     |

| Change to Falling Edge Loop Propagation Delay (TXD to RXI Parameter and Rising Edge Loop Propagation Delay (TXD to | J)  |

| RXD) Parameter, Table 2                                                                                            | . 5 |

| Theory of Operation                                                         |

|-----------------------------------------------------------------------------|

| CAN Transceiver Operation14                                                 |

| Signal Isolation                                                            |

| Integrated and Certified IEC Electromagnetic Compatibility (EMC) Solution14 |

| ±40 V Miswire Protection                                                    |

| Dominant Timeout                                                            |

| Fail-Safe Features                                                          |

| Thermal Shutdown                                                            |

| Applications Information                                                    |

| Radiated Emissions and PCB Layout16                                         |

| PCB Layout16                                                                |

| Thermal Analysis16                                                          |

| Insulation Lifetime                                                         |

| Surface Tracking                                                            |

| Insulation Wear Out                                                         |

| Calculation and Use of Parameters Example                                   |

| Outline Dimensions                                                          |

| Ordering Guide                                                              |

10/2018—Revision 0: Initial Version

# **SPECIFICATIONS**

All voltages are relative to their respective ground,  $1.7~V \le V_{\rm DD1} \le 5.5~V$ ,  $4.5~V \le V_{\rm DD2} \le 5.5~V$ , and  $-40^{\circ}C \le T_{\rm A} \le +125^{\circ}C$ , unless otherwise noted. Typical specifications are at  $V_{\rm DD1} = V_{\rm DD2} = 5~V$  and  $T_{\rm A} = 25^{\circ}C$ , unless otherwise noted.

Table 1.

| Parameter                                                     | Symbol                                | Min                     | Тур | Max                   | Unit | Test Conditions/Comments                                                                                       |

|---------------------------------------------------------------|---------------------------------------|-------------------------|-----|-----------------------|------|----------------------------------------------------------------------------------------------------------------|

| SUPPLY CURRENT                                                |                                       |                         |     |                       |      |                                                                                                                |

| Bus Side                                                      | I <sub>DD2</sub>                      |                         |     |                       |      |                                                                                                                |

| Recessive State                                               |                                       |                         | 5.3 | 7                     | mA   | TXD high, load resistance ( $R_L$ ) = 60 $\Omega$                                                              |

| Dominant State                                                |                                       |                         | 63  | 75                    | mA   | Limited by transmit dominant timeout $(t_{DT})$ , see the Theory of Operation section, $R_L = 60 \Omega$       |

|                                                               |                                       |                         |     | 73                    | mA   | Limited by $t_{DT}$ , $R_L = 60 \Omega$ , $4.75 \text{ V} \leq V_{DD2} \leq 5.25 \text{ V}$                    |

| 70% Dominant/30% Recessive                                    |                                       |                         |     |                       |      | Worst case, see the Theory of Operation section, $R_L = 60\Omega$                                              |

| 1 Mbps                                                        |                                       |                         | 45  | 58                    | mA   |                                                                                                                |

| 5 Mbps                                                        |                                       |                         | 49  | 60                    | mA   |                                                                                                                |

| 12 Mbps                                                       |                                       |                         | 58  | 65                    | mA   |                                                                                                                |

| Logic Side iCoupler Current                                   | I <sub>DD1</sub>                      |                         |     | 5.5                   | mA   | TXD high, low, or switching                                                                                    |

| DRIVER                                                        |                                       |                         |     |                       |      |                                                                                                                |

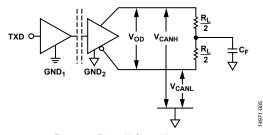

| Differential Outputs                                          |                                       |                         |     |                       |      | See Figure 18                                                                                                  |

| Recessive State Voltage                                       |                                       |                         |     |                       |      | TXD high, R <sub>L</sub> , and common-mode filter capacitor (C <sub>F</sub> ) open                             |

| CANH, CANL                                                    | V <sub>CANL</sub> , V <sub>CANH</sub> | 2.0                     |     | 3.0                   | V    |                                                                                                                |

| Differential Output                                           | V <sub>OD</sub>                       | -500                    |     | +50                   | mV   |                                                                                                                |

| Dominant State Voltage                                        |                                       |                         |     |                       |      | TXD low, C <sub>F</sub> open                                                                                   |

| CANH                                                          | V <sub>CANH</sub>                     | 2.75                    |     | 4.5                   | V    | $50 \Omega \le R_L \le 65 \Omega$                                                                              |

| CANL                                                          | V <sub>CANL</sub>                     | 0.5                     |     | 2.0                   | V    | $50 \Omega \le R_L \le 65 \Omega$                                                                              |

| Differential Output                                           | V <sub>OD</sub>                       | 1.5                     |     | 3.0                   | V    | $50 \Omega \le R_L \le 65 \Omega$                                                                              |

| ·                                                             |                                       | 1.4                     |     | 3.3                   | V    | $45 \Omega \le R_L \le 70$                                                                                     |

|                                                               |                                       | 1.5                     |     | 5.0                   | V    | $R_L = 2240 \Omega$                                                                                            |

| Output Symmetry ( $V_{DD2} - V_{CANH}$ to $V_{CANL}$ )        | V <sub>SYM</sub>                      | -0.55                   |     | +0.55                 | V    | $R_L = 60 \Omega, C_F = 4.7 \text{nF}$                                                                         |

| Short-Circuit Current Absolute                                | Isc                                   |                         |     |                       |      | R <sub>L</sub> open                                                                                            |

| CANH                                                          |                                       |                         |     | 115                   | mA   | $V_{CANH} = -3 V$                                                                                              |

| CANL                                                          |                                       |                         |     | 115                   | mA   | $V_{CANL} = 18 V$                                                                                              |

| Steady State                                                  |                                       |                         |     |                       |      |                                                                                                                |

| CANH                                                          |                                       |                         |     | 115                   | mA   | $V_{CANH} = -24 V$                                                                                             |

| CANL                                                          |                                       |                         |     | 115                   | mA   | $V_{CANL} = 24 V$                                                                                              |

| Logic Input TXD                                               |                                       |                         |     |                       |      |                                                                                                                |

| Input Voltage                                                 |                                       |                         |     |                       |      |                                                                                                                |

| High                                                          | V <sub>IH</sub>                       | 0.65 × V <sub>DD1</sub> |     |                       | V    |                                                                                                                |

| Low                                                           | V <sub>IL</sub>                       |                         |     | $0.35 \times V_{DD1}$ | V    |                                                                                                                |

| Complementary Metal-Oxide<br>Semiconductor (CMOS) Logic Input | і<br> Іін ,  Іі <u>г</u>              |                         |     | 10                    | μΑ   | Input high or low                                                                                              |

| Currents                                                      |                                       |                         |     |                       |      |                                                                                                                |

| RECEIVER                                                      |                                       |                         |     |                       |      |                                                                                                                |

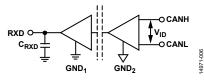

| Differential Inputs                                           |                                       |                         |     |                       |      |                                                                                                                |

| Differential Input Voltage Range                              | V <sub>ID</sub>                       |                         |     |                       |      | See Figure 19, RXD capacitance (C <sub>RXD</sub> ) open, -25 V < V <sub>CANL</sub> , V <sub>CANH</sub> < +25 V |

| Recessive                                                     |                                       | -1.0                    |     | +0.5                  | V    |                                                                                                                |

| Dominant                                                      |                                       | 0.9                     |     | 5.0                   | V    |                                                                                                                |

| Input Voltage Hysteresis                                      | V <sub>HYS</sub>                      |                         | 150 |                       | mV   |                                                                                                                |

| Parameter                                   | Symbol                              | Min                    | Тур | Max   | Unit  | Test Conditions/Comments                                                                  |

|---------------------------------------------|-------------------------------------|------------------------|-----|-------|-------|-------------------------------------------------------------------------------------------|

| Unpowered Input Leakage Current             | I <sub>IN (OFF)</sub>               |                        |     | 10    | μΑ    | $V_{CANH}$ , $V_{CANL} = 5 V$ , $V_{DD2} = 0 V$                                           |

| Input Resistance                            |                                     |                        |     |       |       |                                                                                           |

| CANH, CANL                                  | RINH, RINL                          | 6                      |     | 25    | kΩ    |                                                                                           |

| Differential                                | R <sub>DIFF</sub>                   | 20                     |     | 100   | kΩ    |                                                                                           |

| Input Resistance Matching                   | $m_R$                               | -0.03                  |     | +0.03 |       | $m_R = 2 \times (R_{INH} - R_{INL})/(R_{INH} + R_{INL})$                                  |

| CANH, CANL Input Capacitance                | C <sub>INH</sub> , C <sub>INL</sub> |                        | 35  |       | pF    |                                                                                           |

| Differential Input Capacitance              | C <sub>DIFF</sub>                   |                        | 12  |       | рF    |                                                                                           |

| Logic Output (RXD)                          |                                     |                        |     |       |       |                                                                                           |

| Output Voltage                              |                                     |                        |     |       |       |                                                                                           |

| Low                                         | $V_{OL}$                            |                        | 0.2 | 0.4   | ٧     | Output impedance (I <sub>OUT</sub> ) = 2 mA                                               |

| High                                        | V <sub>OH</sub>                     | V <sub>DD1</sub> – 0.2 |     |       | ٧     | $I_{OUT} = -2 \text{ mA}$                                                                 |

| Short-Circuit Current                       | los                                 | 7                      |     | 85    | mA    | Output voltage $(V_{OUT}) = GND_1$ or $V_{DD1}$                                           |

| COMMON-MODE TRANSIENT IMMUNITY <sup>1</sup> |                                     |                        |     |       |       | Common-mode voltage $(V_{CM}) \ge 1 \text{ kV}$ , transient magnitude $\ge 800 \text{ V}$ |

| Input High, Recessive                       | CM <sub>H</sub>                     | 75                     | 100 |       | kV/μs | Input voltage (V <sub>IN</sub> ) = V <sub>DD1</sub> (TXD) or CANH/CANL recessive          |

| Input Low, Dominant                         | $ CM_L $                            | 75                     | 100 |       | kV/μs | $V_{IN} = 0 V (TXD)$ or CANH/CANL dominant                                                |

<sup>&</sup>lt;sup>1</sup>  $|CM_H|$  is the maximum common-mode voltage slew rate that can be sustained while maintaining CANH/CANL recessive or RXD ≥  $V_{DD1}$  – 0.2 V.  $|CM_L|$  is the maximum common-mode voltage slew rate that can be sustained while maintaining CANH/CANL dominant or RXD ≤ 0.4 V. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges.

# **TIMING SPECIFICATIONS**

All voltages are relative to their respective ground, 1.7 V  $\leq$  V<sub>DD1</sub>  $\leq$  5.5 V, 4.5 V  $\leq$  V<sub>DD2</sub>  $\leq$  5.5 V, and  $-40^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  +125°C, unless otherwise noted. Typical specifications are at V<sub>DD1</sub> = V<sub>DD2</sub> = 5 V and T<sub>A</sub> = 25°C, unless otherwise noted.

Table 2.

| Parameter                                                 | Symbol                 | Min  | Тур | Max  | Unit | Test Conditions/Comments                                                                                   |

|-----------------------------------------------------------|------------------------|------|-----|------|------|------------------------------------------------------------------------------------------------------------|

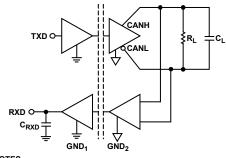

| DRIVER                                                    |                        |      |     |      |      | See Figure 2 and Figure 18, $t_{B\Pi\_TXD} = 200$ ns, $R_L = 60 \Omega$ , $C_L = 100$ pF                   |

| Maximum Data Rate                                         |                        | 12   |     |      | Mbps |                                                                                                            |

| Propagation Delay from TXD to Bus (Recessive to Dominant) | t <sub>TXD_DOM</sub>   |      | 35  | 60   | ns   |                                                                                                            |

| Propagation Delay from TXD to Bus (Dominant to Recessive) | t <sub>TXD_REC</sub>   |      | 45  | 70   | ns   |                                                                                                            |

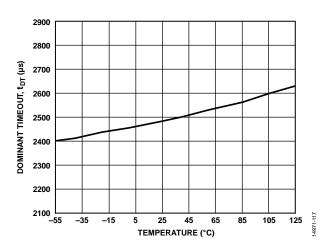

| Transmit Dominant Timeout                                 | t <sub>DT</sub>        | 1175 |     | 4000 | μs   | TXD low, see Figure 3                                                                                      |

| RECEIVER                                                  |                        |      |     |      |      | See Figure 2 and Figure 20, $t_{BIT\_TXD} = 200$ ns, $R_L = 60 \Omega$ , $C_L = 100$ pF, $C_{RXD} = 15$ pF |

| Falling Edge Loop Propagation Delay (TXD to RXD)          | tloop_fall             |      |     | 150  | ns   |                                                                                                            |

| Rising Edge Loop Propagation Delay (TXD to RXD)           | t <sub>LOOP_RISE</sub> |      |     | 150  | ns   |                                                                                                            |

| Loop Delay Symmetry (Minimum Recessive Bit Width)         | t <sub>BIT_RXD</sub>   |      |     |      |      |                                                                                                            |

| 2 Mbps                                                    |                        | 450  |     | 550  | ns   | t <sub>BIT_TXD</sub> = 500 ns                                                                              |

| 5 Mbps                                                    |                        | 160  |     | 220  | ns   | $t_{BIT\_TXD} = 200 \text{ ns}$                                                                            |

| 8 Mbps                                                    |                        | 85   |     | 140  | ns   | $t_{BIT\_TXD} = 125 \text{ ns}$                                                                            |

| 12 Mbps                                                   |                        | 50   |     | 91.6 | ns   | $t_{BIT\_TXD} = 83.3 \text{ ns}$                                                                           |

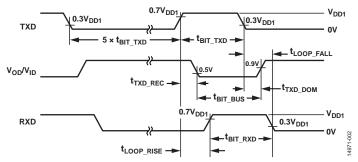

## **TIMING DIAGRAMS**

Figure 2. Transceiver Timing Diagram

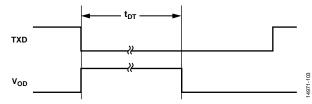

Figure 3. Dominant Timeout,  $t_{DT}$

## **INSULATION AND SAFETY RELATED SPECIFICATIONS**

For additional information, see www.analog.com/icouplersafety.

Table 3.

| Parameter                                                                   | Symbol  | Value | Unit   | Test Conditions/Comments                                                                                                   |

|-----------------------------------------------------------------------------|---------|-------|--------|----------------------------------------------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage                                         |         | 5700  | V rms  | 1-minute duration                                                                                                          |

| Minimum External Air Gap (Clearance)                                        | L (I01) | 7.8   | mm min | Measured from input terminals to output terminals, shortest distance through air                                           |

| Minimum External Tracking (Creepage)                                        | L (102) | 7.8   | mm min | Measured from input terminals to output terminals, shortest distance path along body                                       |

| Minimum Clearance in the Plane of the Printed Circuit Board (PCB) Clearance | L (PCB) | 8.3   | mm min | Measured from input terminals to output terminals, shortest distance through air, line of sight, in the PCB mounting plane |

| Minimum Internal Gap (Internal Clearance)                                   |         | 25.5  | μm min | Insulation distance through insulation                                                                                     |

| Tracking Resistance (Comparative Tracking Index)                            | CTI     | >600  | V      | DIN IEC 112/VDE 0303 Part 1                                                                                                |

| Material Group                                                              |         | 1     |        | Material group (DIN VDE 0110, 1/89, Table 1)                                                                               |

## **PACKAGE CHARACTERISTICS**

Table 4.

| Parameter                                  | Symbol           | Min | Тур              | Max | Unit | Test Conditions/Comments |

|--------------------------------------------|------------------|-----|------------------|-----|------|--------------------------|

| Resistance (Input to Output) <sup>1</sup>  | R <sub>I-O</sub> |     | 10 <sup>13</sup> |     | Ω    |                          |

| Capacitance (Input to Output) <sup>1</sup> | C <sub>I-O</sub> |     | 1.1              |     | рF   | f = 1 MHz                |

| Input Capacitance <sup>2</sup>             | Cı               |     | 4.0              |     | рF   |                          |

<sup>&</sup>lt;sup>1</sup> The device is considered a two-terminal device: Pin 1 through Pin 8 are shorted together, and Pin 9 through Pin 16 are shorted together.

### **REGULATORY INFORMATION**

See Table 9 and the Insulation Lifetime section for the recommended maximum working voltages for specific cross isolation waveforms and insulation levels. The ADM3050E is pending approval or approved by the organizations listed in Table 5.

Table 5.

| UL (Pending)                                         | CSA (Pending)                                                                          | VDE (Pending)                                                                              | CQC (Pending)                                               |

|------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| UL1577 Component<br>Recognition Program <sup>1</sup> | Approved under CSA Component<br>Acceptance Notice 5A                                   | DIN V VDE V 0884-10<br>(VDE V 0884-10):2006-12 <sup>2</sup>                                | Certified under CQC11-<br>471543-2012                       |

| Single Protection, 5700 V rms<br>Isolation Voltage   | CSA 60950-1-07+A1+A2 and IEC 60950-1, second edition, +A1+A2:                          | Reinforced insulation,<br>849 V <sub>PEAK</sub> , V <sub>IOTM</sub> = 8 kV <sub>PEAK</sub> | GB4943.1-2011                                               |

|                                                      | Basic insulation at 780 V rms (1103 V <sub>PEAK</sub> )                                |                                                                                            | Basic insulation at 780 V rms (1103 V <sub>PEAK</sub> )     |

|                                                      | Reinforced insulation at 390 V rms (552 V <sub>PEAK</sub> )                            |                                                                                            | Reinforced insulation at 390 V rms (552 V <sub>PEAK</sub> ) |

|                                                      | IEC 60601-1 Edition 3.1:                                                               |                                                                                            |                                                             |

|                                                      | Basic insulation (1 MOPP), 490 V rms (686 V <sub>PEAK</sub> )                          |                                                                                            |                                                             |

|                                                      | Reinforced insulation (2 MOPP), 238 V rms<br>(325 V <sub>PEAK</sub> )                  |                                                                                            |                                                             |

|                                                      | CSA 61010-1-12 and IEC 61010-1 third edition:                                          |                                                                                            |                                                             |

|                                                      | Basic insulation at: 300 V rms mains, 780 V secondary (1103 V <sub>PEAK</sub> )        |                                                                                            |                                                             |

|                                                      | Reinforced insulation at: 300 V rms mains,<br>390 V secondary (552 V <sub>PEAK</sub> ) |                                                                                            |                                                             |

| File E214100                                         | File 205078                                                                            | File 2471900-4880-0001                                                                     | File (pending)                                              |

$<sup>^{1}</sup>$  In accordance with UL 1577, each ADM3050E is proof tested by applying an insulation test voltage  $\geq$  6840 V rms for 1 sec.

<sup>&</sup>lt;sup>2</sup> Input capacitance is from any input data pin to ground.

<sup>&</sup>lt;sup>2</sup> In accordance with DIN V VDE V 0884-10, each product is proof tested by applying an insulation test voltage ≥ 1592 V peak for 1 sec (partial discharge detection limit = 5 pC). The \* marking branded on the component designates DIN V VDE V 0884-10 approval.

# DIN V VDE V 0884-10 (VDE V 0884-10) INSULATION CHARACTERISTICS (PENDING)

These isolators are suitable for reinforced electrical isolation only within the safety limit data. Protective circuits ensure the maintenance of the safety data.

## Table 6.

| Description                                                 | Test Conditions/Comments                                                                                                                                                                                                   | Symbol                | Characteristic | Unit              |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|-------------------|

| Installation Classification per DIN VDE 0110                |                                                                                                                                                                                                                            |                       |                |                   |

| For Rated Mains Voltage ≤ 150 V rms                         |                                                                                                                                                                                                                            |                       | I to IV        |                   |

| For Rated Mains Voltage ≤ 300 V rms                         |                                                                                                                                                                                                                            |                       | I to IV        |                   |

| For Rated Mains Voltage ≤ 600 V rms                         |                                                                                                                                                                                                                            |                       | I to IV        |                   |

| Climatic Classification                                     |                                                                                                                                                                                                                            |                       | 40/125/21      |                   |

| Pollution Degree per DIN VDE 0110, Table 1                  |                                                                                                                                                                                                                            |                       | 2              |                   |

| Maximum Working Insulation Voltage<br>Reinforced            |                                                                                                                                                                                                                            | V <sub>IORM</sub>     | 849            | V <sub>PEAK</sub> |

| Basic, DC Working Voltage                                   | See the Absolute Maximum Ratings section and Table 9 for<br>the maximum continuous working voltage for ac bipolar,<br>ac unipolar, and dc voltages, basic and reinforced insulation,<br>and 50 year lifetime to 1% failure | V <sub>IORM(DC)</sub> | 1500           | V <sub>DC</sub>   |

| Input to Output Test Voltage, Method B1                     | $V_{IORM} \times 1.875 = V_{pd (m)}$ , 100% production test, $t_{ini} = t_m = 1$ sec, partial discharge $< 5$ pC                                                                                                           | V <sub>pd (m)</sub>   | 1592           | $V_{PEAK}$        |

| Input to Output Test Voltage, Method A                      |                                                                                                                                                                                                                            | $V_{pd (m)}$          |                |                   |

| After Environmental Tests Subgroup 1                        | $V_{IORM} \times 1.5 = V_{pd (m)}$ , $t_{ini} = 60$ sec, $t_m = 10$ sec, partial discharge $< 5$ pC                                                                                                                        |                       | 1274           | $V_{PEAK}$        |

| After Input and/or Safety Test<br>Subgroup 2 and Subgroup 3 | $V_{IORM} \times 1.2 = V_{pd (m)}$ , $t_{ini} = 60$ sec, $t_m = 10$ sec, partial discharge $< 5$ pC                                                                                                                        |                       | 1019           | V <sub>PEAK</sub> |

| Highest Allowable Overvoltage                               |                                                                                                                                                                                                                            | V <sub>IOTM</sub>     | 8000           | $V_{PEAK}$        |

| Impulse                                                     | 1.2 μs rise time, 50 μs, 50% fall time in air to the preferred sequence                                                                                                                                                    | VIMPULSE              | 8000           | V <sub>PEAK</sub> |

| Surge Isolation Voltage                                     |                                                                                                                                                                                                                            |                       |                | $V_{PEAK}$        |

| Basic                                                       | $V_{PEAK}$ = 12.8 kV, 1.2 $\mu$ s rise time, 50 $\mu$ s, and 50% fall time                                                                                                                                                 | $V_{IOSM}$            | 12000          | $V_{PEAK}$        |

| Reinforced                                                  | $V_{PEAK} = 12.8$ kV, 1.2 $\mu$ s rise time, 50 $\mu$ s, and 50% fall time                                                                                                                                                 | V <sub>IOSM</sub>     | 8000           | $V_{PEAK}$        |

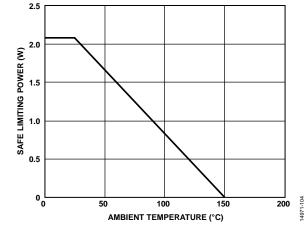

| Safety Limiting Values                                      | Maximum value allowed in the event of a failure (see Figure 4)                                                                                                                                                             |                       |                |                   |

| Maximum Junction Temperature                                |                                                                                                                                                                                                                            | Ts                    | 150            | °C                |

| Total Power Dissipation at 25°C                             |                                                                                                                                                                                                                            | Ps                    | 2.08           | W                 |

| Insulation Resistance at T <sub>S</sub>                     | Test voltage = 500 V                                                                                                                                                                                                       | Rs                    | >109           | Ω                 |

Figure 4. Thermal Derating Curve, Dependence of Safety Limiting Values with Ambient Temperature per DIN V VDE V 0884-10 (See the Thermal Resistance Section for Additional Information)

# **ABSOLUTE MAXIMUM RATINGS**

Pin voltages with respect to  $GND_1/GND_2$  are on same side, unless otherwise noted.

Table 7.

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                    |                                             |

|------------------------------------------------------------|---------------------------------------------|

| Parameter                                                  | Rating                                      |

| V <sub>DD1</sub> /V <sub>DD2</sub>                         | −0.5 V to +6 V                              |

| Logic Side Input and Output: TXD, RXD                      | $-0.5 \text{ V to V}_{DD1} + 0.5 \text{ V}$ |

| CANH, CANL                                                 | -40 V to +40 V                              |

| Operating Temperature Range                                | −40°C to +125°C                             |

| Storage Temperature Range                                  | −65°C to +150°C                             |

| Maximum Junction Temperature (T <sub>J</sub> )             | 150°C                                       |

| Electrostatic Discharge (ESD),<br>IEC 61000-4-2, CANH/CANL |                                             |

| Across Isolation Barrier with Respect to $GND_1$           | ±8 kV                                       |

| Contact Discharge with Respect to GND <sub>2</sub>         | ±8 kV typical                               |

| Air Discharge with Respect to GND <sub>2</sub>             | ±15 kV                                      |

| Human Body Model (HBM), All Pins, 1.5 kΩ, 100 pF           | ±4 kV                                       |

| Moisture Sensitivity Level (MSL)                           | 3                                           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.

**Table 8. Thermal Resistance**

| Package Type <sup>1</sup> | θ <sub>JA</sub> | Unit |

|---------------------------|-----------------|------|

| RW-16                     | 60              | °C/W |

<sup>&</sup>lt;sup>1</sup> The thermocouple is located at the center of the package underside, and the test was conducted on a 4-layer board with thin traces. See the Thermal Analysis section for the thermal model definitions.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

Table 9. Maximum Continuous Working Voltage<sup>1</sup>

| Parameter             | Insulation Rating (20-Year Lifetime) <sup>2</sup> | VDE 0884-11 Lifetime Conditions Fulfilled               |

|-----------------------|---------------------------------------------------|---------------------------------------------------------|

| AC Voltage            |                                                   |                                                         |

| Bipolar Waveform      |                                                   |                                                         |

| Basic Insulation      | 849 V <sub>PEAK</sub>                             | Lifetime limited by insulation lifetime per VDE-0884-11 |

| Reinforced Insulation | 707 V <sub>PEAK</sub>                             | Lifetime limited by insulation lifetime per VDE-0884-11 |

| Unipolar Waveform     |                                                   |                                                         |

| Basic Insulation      | 1697 V <sub>PEAK</sub>                            | Lifetime limited by insulation lifetime per VDE-0884-11 |

| Reinforced Insulation | 1275 V <sub>PEAK</sub>                            | Lifetime limited by package creepage per IEC 60664-1    |

| DC Voltage            |                                                   |                                                         |

| Basic Insulation      | 1560 V <sub>PEAK</sub>                            | Lifetime limited by package creepage per IEC 60664-1    |

| Reinforced Insulation | 780 V <sub>PEAK</sub>                             | Lifetime limited by package creepage per IEC 60664-1    |

<sup>&</sup>lt;sup>1</sup> The maximum continuous working voltage refers to the continuous voltage magnitude imposed across the isolation barrier. See the Insulation Lifetime section for more details.

<sup>&</sup>lt;sup>2</sup> Insulation capability without regard to creepage limitations. Working voltage may be limited by the PCB creepage when considering rms voltages for components soldered to a PCB (assumes Material Group I up to 1250 V rms), or by the SOIC\_W package creepage of 7.8 mm, when considering rms voltages for Material Group II.

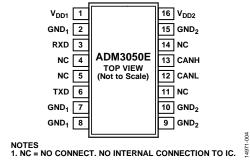

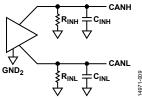

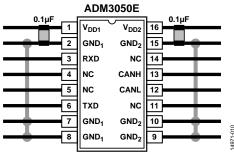

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 5. Pin Configuration

**Table 10. Pin Function Descriptions**

| Pin No.      | Mnemonic         | Description                                                                                |  |

|--------------|------------------|--------------------------------------------------------------------------------------------|--|

| 1            | V <sub>DD1</sub> | Power Supply, Logic Side, 1.7 V to 5.5 V. This pin requires a 0.1 µF decoupling capacitor. |  |

| 2, 7, 8      | GND <sub>1</sub> | Ground, Logic Side.                                                                        |  |

| 3            | RXD              | Receiver Output Data.                                                                      |  |

| 4, 5, 11, 14 | NC               | No Connect. No internal connection to IC.                                                  |  |

| 6            | TXD              | Driver Input Data.                                                                         |  |

| 9, 10, 15    | GND <sub>2</sub> | Ground, Bus Side.                                                                          |  |

| 12           | CANL             | CAN Low Input and Output.                                                                  |  |

| 13           | CANH             | CAN High Input and Output.                                                                 |  |

| 16           | $V_{DD2}$        | Power Supply, Bus Side, 4.5 V to 5.5 V. This pin requires a 0.1 μF decoupling capacitor.   |  |

# **OPERATIONAL TRUTH TABLE**

Table 11. Truth Table

| V <sub>DD1</sub> | V <sub>DD2</sub> | TXD        | Mode            | RXD           | CANH/CANL                              |

|------------------|------------------|------------|-----------------|---------------|----------------------------------------|

| On               | On               | Low        | Normal          | Low           | Dominant (limited by t <sub>DT</sub> ) |

| On               | On               | High       | Normal          | High per bus  | Recessive and set by bus               |

| Off              | On               | Don't care | Normal          | Indeterminate | Recessive and set by bus               |

| On               | Off              | Don't care | Transceiver off | High          | High-Z                                 |

# TYPICAL PERFORMANCE CHARACTERISTICS

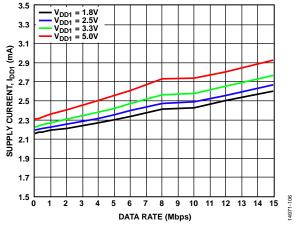

Figure 6. Supply Current (IDD1) vs. Data Rate

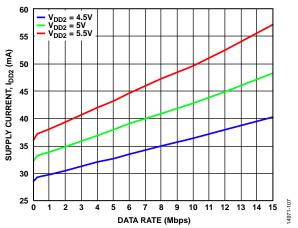

Figure 7. Supply Current (IDD2) vs. Data Rate

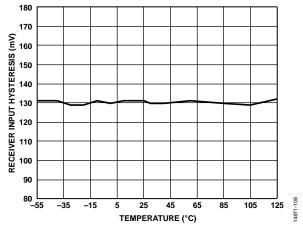

Figure 8. Receiver Input Hysteresis vs. Temperature

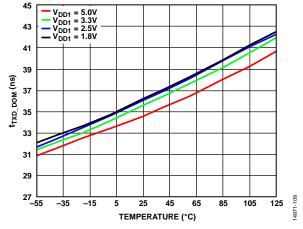

Figure 9. t<sub>TXD\_DOM</sub> vs. Temperature

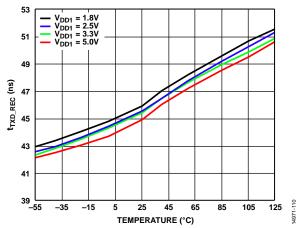

Figure 10. t<sub>TXD\_REC</sub> vs. Temperature

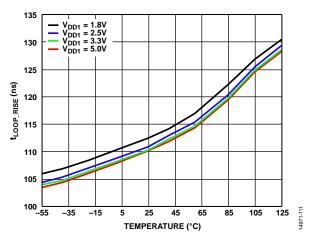

Figure 11. t<sub>LOOP\_RISE</sub> vs. Temperature

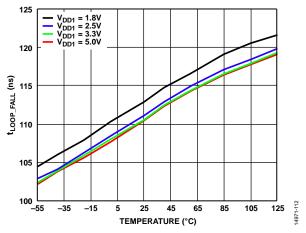

Figure 12.  $t_{\text{LOOP\_FALL}}$  vs. Temperature

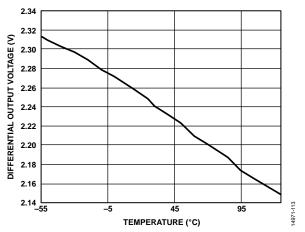

Figure 13. Differential Output Voltage vs. Temperature,  $R_L = 60 \Omega$

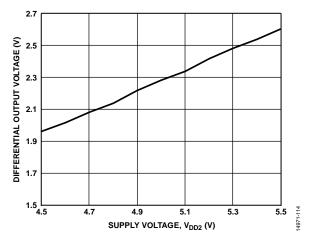

Figure 14. Differential Output Voltage vs. Supply Voltage ( $V_{DD2}$ ),  $R_L = 60 \Omega$

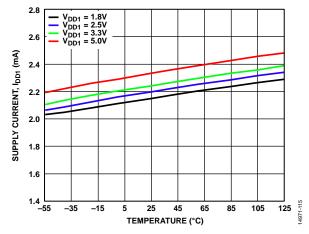

Figure 15. Supply Current (IDD1) vs. Temperature

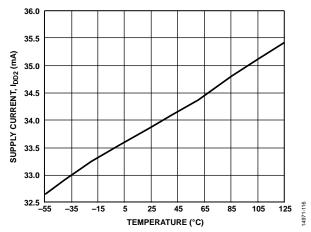

Figure 16. Supply Current (IDD2) vs. Temperature

Figure 17. Dominant Timeout (t<sub>DT</sub>) vs. Temperature

# **TEST CIRCUITS**

Figure 18. Driver Voltage Measurement

Figure 19. Receiver Voltage Measurement

1. 1% TOLERANCE FOR ALL RESISTORS AND CAPACITORS.

Figure 20. Switching Characteristics Measurements

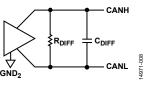

Figure 21. RDIFF and CDIFF Measured in Recessive State, Bus Disconnected

Figure 22. Input Resistance (R<sub>INX</sub>) and Input Capacitance (C<sub>INX</sub>) Measured in Recessive State, Bus Disconnected

# **TERMINOLOGY**

#### IDD1

$I_{DD1}$  is the current drawn by the  $V_{DD1}$  pin.

#### $I_{DD2}$

$I_{DD2}$  is the current drawn by the  $V_{DD1}$  pin.

#### $V_{\text{OD}}$ and $V_{\text{ID}}$

$V_{\text{OD}}$  and  $V_{\text{ID}}$  are the differential voltages from the transmitter or at the receiver on the CANH and CANL pins.

#### TXD DOM

$t_{\text{TXD\_DOM}}$  is the propagation delay from a low signal on TXD to transition the bus to a dominant state.

#### $t_{\text{TXD\_REC}}$

$t_{\text{TXD\_REC}}$  is the propagation delay from a high signal on TXD to transition the bus to a recessive state.

#### **t**loop fall

$t_{\text{LOOP\_FALL}}$  is the propagation delay of a low signal on the TXD pin to the bus dominant.  $t_{\text{ON\_LOOP}}$  transitions low on the RXD pin.

#### $t_{\text{LOOP\_RISE}}$

$t_{\text{LOOP\_RISE}}$  is the propagation delay of a high signal on TXD to the bus recessive.  $t_{\text{OFF\_LOOP}}$  transitions high on the RXD pin.

#### t<sub>BIT TXD</sub>

$t_{BIT\_TXD}$  is the bit time at the TXD pin as transmitted by the CAN controller. See Figure 2 for level definitions.

#### tBIT BU

$t_{BIT\_BUS}$  is the bit time as transmitted by the transceiver to the bus. When compared with a given  $t_{BIT\_TXD}$ , a measure of bit symmetry from the TXD digital isolation channel and CAN transceiver can be determined. See Figure 2 for level definitions.

#### tbit rxi

$t_{BIT\_RXD}$  is the bit time on the RXD output pin, which can be compared with  $t_{BIT\_TXD}$  for a round trip measure of pulse width distortion through the TXD digital isolation channel, the CAN transceiver, and back through the RXD isolation channel.

# THEORY OF OPERATION CAN TRANSCEIVER OPERATION

The ADM3050E facilitates communication between a CAN controller and the CAN bus. The CAN controller and the ADM3050E communicate with standard 1.8 V, 2.5 V, 3.3 V or 5.0 V CMOS levels. The internal transceiver translates the CMOS levels to and from the CAN bus.

The CAN bus has two states: dominant and recessive. The recessive state is present on the bus when the differential voltage between CANH and CANL is less than 0.5 V. In the recessive state, both the CANH pin and CANL pin are set to high impedance and are loosely biased to a single-ended voltage of 2.5 V. A dominant state is present on the bus when the differential voltage between CANH and CANL is greater than 1.5 V. The transceiver transmits a dominant state by driving the single-ended voltage of the CANH line to 3.5 V and the CANL pin to 1.5 V. The recessive and dominant states correspond to CMOS high and CMOS low, respectively, on the RXD pin and TXD pin.

A dominant state from another node overwrites a recessive state on the bus. A CAN frame can be set for higher priority by using a longer string of dominant bits to gain control of the CAN bus during the arbitration phase. While transmitting, a CAN transceiver also reads back the state of the bus. When a CAN controller receives a dominant state while transmitting a recessive state during arbitration, the CAN controller surrenders the bus to the node still transmitting the dominant state. The node that gains control during the arbitration phase reads back only its own transmission. This interaction between recessive and dominant states allows competing nodes to negotiate for control of the bus while avoiding contention between nodes.

Industrial applications can have long cable runs. These long runs may have differences in local earth potential. Different sources may also power nodes. The ADM3050E transceiver has a  $\pm 25~\rm V$  common-mode range (CMR) that exceeds the ISO11898-2 requirement and further increases the tolerance to ground variation.

See the AN-1123 Application Note for additional information on CAN.

#### **SIGNAL ISOLATION**

The ADM3050E device provides galvanic signal isolation implemented on the logic side of the interface. The RXD and TXD channels are isolated using a low propagation delay on/off keying (OOK) architecture with *i*Coupler digital isolation technology.

The low propagation delay isolation, quick transceiver conversion speeds, and integrated form factor are critical for longer cable lengths, higher data speeds, and reducing the total solution board space. The ADM3050E isolated transceiver reduces solution board space while increasing data transfer rates over discrete optocoupler and transceiver solutions.

# INTEGRATED AND CERTIFIED IEC ELECTROMAGNETIC COMPATIBILITY (EMC) SOLUTION

Typically, designers must add protections against harsh operating environments while also making the product as small as possible. To reduce the board space and the design efforts needed to meet system level ESD standards, the ADM3050E isolated transceiver has brought robust protection circuitry on-chip for the CANH and CANL lines.

#### ±40 V MISWIRE PROTECTION

High voltage miswire events commonly occur when the system power supply is connected directly to the CANH and the CANL bus lines during assembly. Supplies may also be shorted by accidental damage to the field bus cables while the system is operating. Accounting for inductive kick and switching effects, the ADM3050E isolated transceiver CAN bus lines are protected against these miswire or shorting events in systems with up to nominal 24 V supplies. The CANH and CANL signal lines can withstand a continuous supply short with respect to GND2 or between the CAN bus lines without damage. This level of protection applies when the device is either powered or unpowered.

#### **DOMINANT TIMEOUT**

The ADM3050E features a dominant timeout ( $t_{\rm DT}$  in Figure 3). A TXD line shorted to ground, or malfunctioning CAN controller are examples of how a single node can indefinitely prevent further bus traffic.  $t_{\rm DT}$  limits how long the dominant state can transmit to the CAN bus by the transceiver. The TXD function restores when the line is presented with a logic low.

The  $t_{\rm DT}$  minimum also inherently creates a minimum data rate. Under normal operation, the CAN protocol allows five consecutive bits of the same polarity before stuffing a bit of opposite polarity into the transmitting bit sequence. When an error is detected, the CAN controller purposely violates the bit stuffing rules by producing six consecutive dominant bits. At any given data rate, the CAN controller must transmit as many as 11 consecutive dominant bits to effectively limit the ADM3050E minimum data rate to 9600 bps.

### **FAIL-SAFE FEATURES**

In cases where the TXD input pin is allowed to float to prevent bus traffic interruption, the TXD input channel has an internal pull-up to the  $V_{\rm DD1}$  pin. The pull-up holds the transceiver in the recessive state.

# **THERMAL SHUTDOWN**

The integrated transceiver is designed with thermal shutdown circuitry to protect the device from excessive power dissipation during fault conditions. Shorting the driver outputs to a low impedance source can result in high driver currents. The thermal

sensing circuitry detects the increase in die temperature under this condition and disables the driver outputs. The circuitry disables the driver outputs when the die temperature reaches 175°C. The drivers are enabled after the die has cooled.

# APPLICATIONS INFORMATION RADIATED EMISSIONS AND PCB LAYOUT

The ADM3050E isolated CAN transceivers with integrated dc-to-dc converters pass EN 55022, Class B by 6 dB on a simple 2-layer PCB design. Neither stitching capacitance nor high voltage surface mount (SMT) safety capacitors are required to meet this emission level.

#### **PCB LAYOUT**

The ADM3050E isolated CAN transceiver requires no external interface circuitry for the logic interfaces. Power supply bypassing is required at the logic input supply  $(V_{\rm DD1})$ , and the shared CAN transceiver and digital isolator supply pin  $(V_{\rm DD2})$ . The recommended bypass capacitor value is 0.1  $\mu F$ . Note that low effective series resistance (ESR) bypass capacitors are required and must be placed as close to the chip pads as possible. The total lead length between both ends of the capacitor and the input power supply pin must not exceed 10 mm. Bypassing between Pin 1, Pin 7, and Pin 8 and between Pin 16, Pin 10, and Pin 9 must also be considered, unless the ground pair on each package side is connected in close proximity to the package.

In applications involving high common-mode transients, minimize board coupling across the isolation barrier. Design the board layout so that any coupling that does occur equally affects all pins on a given component side. Failure to ensure this equal coupling can cause voltage differentials between pins exceeding the absolute maximum ratings of the device, thereby leading to latch-up or permanent damage.

Figure 23. Recommended PCB Layout

## THERMAL ANALYSIS

The ADM3050E device consists of three internal die attached to a split lead frame. For the purposes of thermal analysis, the die are treated as a thermal unit, with the highest junction temperature reflected in the  $\theta_{JA}$  value from Table 8. The  $\theta_{JA}$  value is based on measurements taken with the devices mounted on a JEDEC standard, 4-layer board with fine width traces and still air.

#### **INSULATION LIFETIME**

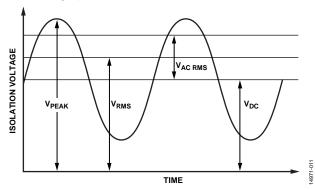

All insulation structures eventually break down when subjected to voltage stress over a sufficiently long period of time. The rate of insulation degradation is dependent on the characteristics of the voltage waveform applied across the insulation as well as on the materials and material interfaces.

The two types of insulation degradation of primary interest are breakdown along surfaces exposed to the air and insulation wear out. Surface breakdown is the phenomenon of surface tracking and is the primary determinant of surface creepage requirements in system level standards. Insulation wear out is the phenomenon where charge injection or displacement currents inside the insulation material cause long-term insulation degradation.

# **SURFACE TRACKING**

Surface tracking is addressed in electrical safety standards by setting a minimum surface creepage based on the working voltage, the environmental conditions, and the properties of the insulation material. Safety agencies perform characterization testing on the surface insulation of components, allowing the components to be categorized in different material groups. Lower material group ratings are more resistant to surface tracking and can therefore provide adequate lifetime with smaller creepage. The minimum creepage for a given working voltage and material group is in each system level standard and is based on the total rms voltage across the isolation, pollution degree, and material group.

The material group and creepage for the ADM3050E isolator is listed in Table 3 for the 16-lead, wide body SOIC package.

## **INSULATION WEAR OUT**

The lifetime of insulation caused by wear out is determined by its thickness, material properties, and the voltage stress applied. It is important to verify that the product lifetime is adequate at the application working voltage. The working voltage supported by an isolator for wear out may not be the same as the working voltage supported for tracking. The working voltage applicable to tracking is specified in most standards.

Testing and modeling have shown that the primary driver of long-term degradation is displacement current in the polyimide insulation causing incremental damage. The stress on the insulation can be broken down into broad categories, such as dc stress, which causes very little wear out because there is no displacement current, and an ac component time varying voltage stress, which causes wear out.

The ratings in certification documents are usually based on 60 Hz sinusoidal stress because this reflects isolation from line voltage. Many practical applications have combinations of 60 Hz ac and dc across the barrier, as shown in Equation 1. Because only the ac portion of the stress causes wear out, the equation can be rearranged to solve for the ac rms voltage, as shown in Equation 2. For insulation wear out with the polyimide materials used in these products, the ac rms voltage determines the product lifetime.

$$V_{RMS} = \sqrt{{V_{AC}}_{RMS}^2 + {V_{DC}}^2}$$

(1)

or

$$V_{ACRMS} = \sqrt{V_{RMS}^2 - V_{DC}^2}$$

(2)

where:

$V_{RMS}$  is the total rms working voltage.

$V_{AC\,RMS}$  is the time varying portion of the working voltage.  $V_{DC}$  is the dc offset of the working voltage.

# CALCULATION AND USE OF PARAMETERS EXAMPLE

The following example frequently arises in power conversion applications. Assume that the line voltage on one side of the isolation is 240 V ac rms and a 400  $V_{\rm DC}$  bus voltage is present on the other side of the isolation barrier. The isolator material is polyimide. To establish the critical voltages in determining the creepage, clearance, and lifetime of a device, see Figure 24 and the following equations.

Figure 24. Critical Voltage Example

The working voltage across the barrier from Equation 1 is

$$V_{RMS} = \sqrt{V_{AC\,RMS}^2 + V_{DC}^2}$$

$$V_{RMS} = \sqrt{240^2 + 400^2}$$

$$V_{RMS} = 466 \text{ V}$$

This  $V_{RMS}$  value is the working voltage used together with the material group and pollution degree when looking up the creepage required by a system standard.

To determine if the lifetime is adequate, obtain the time varying portion of the working voltage. To obtain the ac rms voltage, use Equation 2.

$$V_{AC\,RMS} = \sqrt{{V_{RMS}}^2 - {V_{DC}}^2}$$

$$V_{ACRMS} = \sqrt{466^2 - 400^2}$$

$$V_{ACRMS} = 240 \text{ V rms}$$

In this case, the ac rms voltage is simply the line voltage of  $240\,\mathrm{V}$  rms. This calculation is more relevant when the waveform is not sinusoidal. The value is compared to the limits for working voltage in Table 9 for the expected lifetime, which is less than a  $60\,\mathrm{Hz}$  sine wave, and is well within the limit for a  $50\-\mathrm{year}$  service life.

Note that the dc working voltage limit is set by the creepage of the package as specified in IEC 60664-1. This value can differ for specific system level standards.

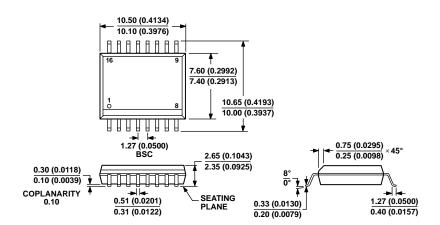

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MS-013-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 25. 16-Lead Standard Small Outline Package [SOIC\_W] Wide Body (RW-16) Dimensions shown in millimeters and (inches)

## **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                             | Package Option |

|--------------------|-------------------|-------------------------------------------------|----------------|

| ADM3050EBRWZ       | −40°C to +125°C   | 16-Lead Standard Small Outline Package [SOIC_W] | RW-16          |

| ADM3050EBRWZ-RL    | -40°C to +125°C   | 16-Lead Standard Small Outline Package [SOIC_W] | RW-16          |

| EVAL-ADM3050EEBZ   |                   | Evaluation Board                                |                |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.